- 全部

- 默认排序

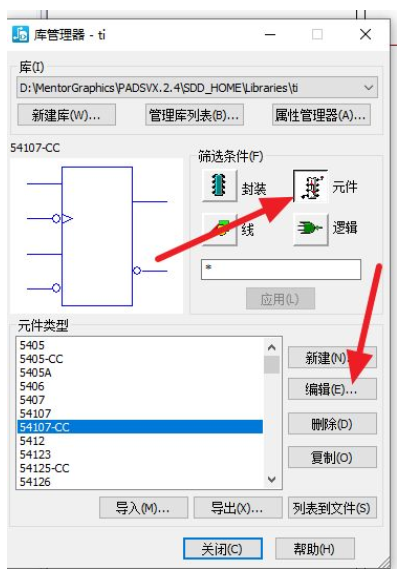

在Logic中,多part器件意味着含有多个CAE封装,用户可以单独查看并修改其中单个的CAE封装。第一步:执行菜单命令文件-库,打开库管理器,点击元件按钮,找到所需要修改的多part器件,点击编辑,如图1所示图1 编辑元件示意图第二步:进

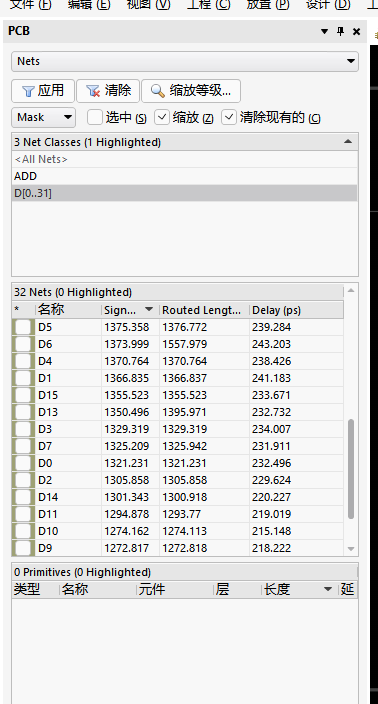

数据线高八位和第八位没有单独创建class,9根线为一组2.地址线,时钟,控制为一组3.pcb上存在短路4.地址线之间需要满足3W间距5.一层连通无需打孔6.电源和地需要处理一下7.注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速PC

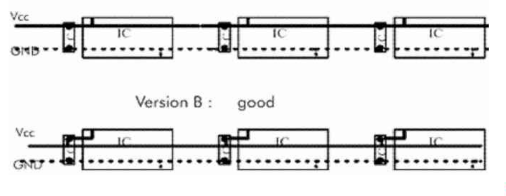

电源和地是高速PCB设计中的重要对象,它们的布局布线处理好坏直接决定着成品的性能运行和串扰大小,若是稍有不慎,很容易拖慢项目进度。所以下面讲讲电源和地的高速PCB布线处理方法,希望对小伙伴们有所帮助。第一,尽量给出单独的电源层和地层;即使要

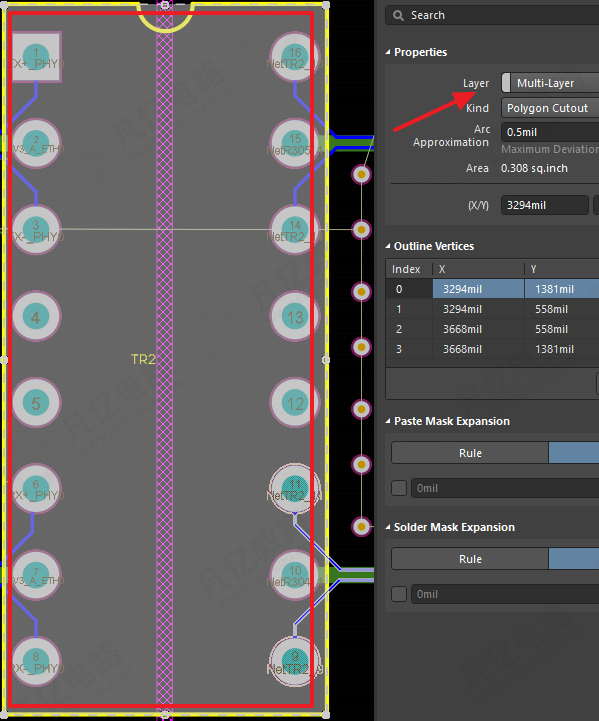

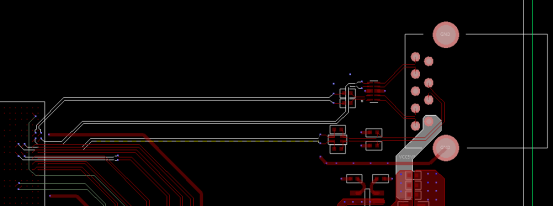

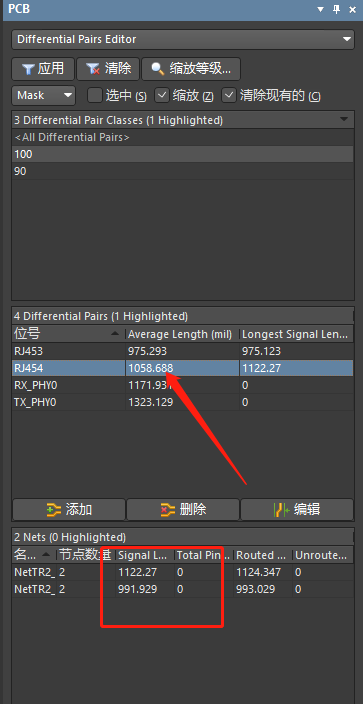

1.变压器下方需要在所有层单独放置铺铜挖空,例如顶层放一个底层再放一个铺铜挖空。2.电源电容的输入输出都需要加粗载流。3.顶底层需要整版铺地铜处理4.TX等长组需要建立xSignals,前后段合并一起等长5.差分对内等长误差要控制在5mil

1.小的滤波电容应该靠近管脚放置2.所有层挖空处理,负片层需要单独放置一个铺铜挖空3.存在开路4.器件摆放尽量不要太近,建议最少1.5mm以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

在PCB设计和制造过程中,存在着许多专业主语,其中之一便是V-cut(V型切割),V-cut是很多工程师常用的切割方式,可将多层PCB分割成单独的板块,但有很多人没听说过,所以本文将详谈V-cut的定义、应用及注意事项。1、V-cut的定义

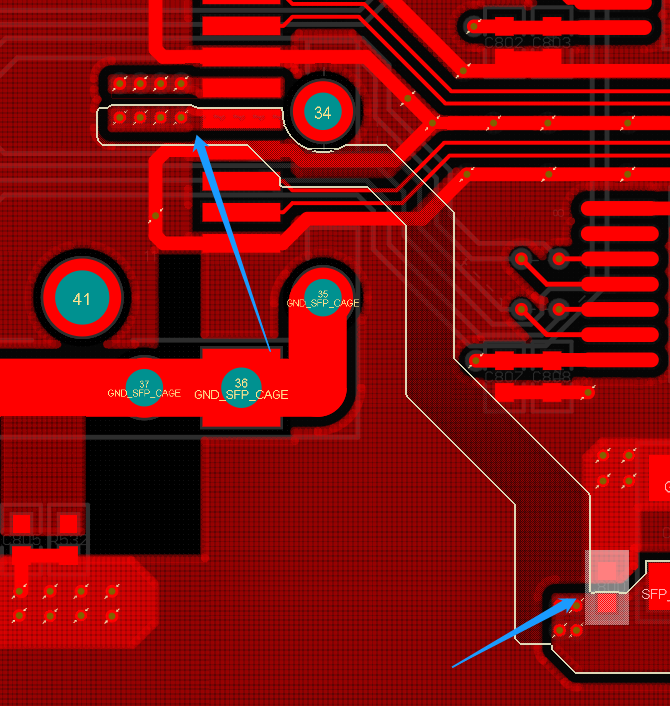

1.差分布线没有包地,需要每对差分单独包地打孔处理 2.差分换层旁边需要靠近打两个地过孔z3.差分布线长距离不耦合 4.差分没有等长,需要分组等长和对内等长处理 5.差分信号布线造成回路,应放置在后面尽量保持信号流向顺畅。 6. 存在飞线没

网口差分需要进行对内等长,误差5mil2.差分走线要尽量耦合3.差分走线可以在进行一下优化4.时钟信号需要单独包地处理5.电容尽量靠近管脚摆放6.此处走线尽量与焊盘同宽,拉出来再进行加粗,加粗尽量渐变,不要突然变很大7.中间可以多打过孔进行

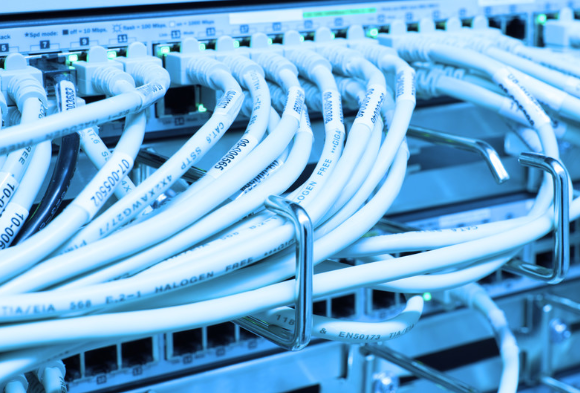

电缆是数据中心中最常见的物体。不幸的是,他们也可能是最丑陋和最难对付的。一个中等规模的数据中心很容易包含数以千计的各种类型的单独电源和网络电缆,如果您不将它们组织好,您的数据中心可能最终看起来像一个愚蠢的线缆战场。更糟糕的是,您可能不知道哪

一、W25M02GW1.8V 2G位(2 X 1G位)串行SLC NAND闪存1、简介:W25M02GW(2 X 1G位)串行MCP(多芯片封装)闪存基于W25N串行SLC NAND SpiFlash®系列,将两个单独的W25N01GW芯片

扫码关注

扫码关注