- 全部

- 默认排序

VDD是我们在电路分析、芯片分析以及电子元件引脚分析时,经常会遇到的一个英文缩写。那么你了解他吗?本期电子技术术语大揭秘为大家详细分析。

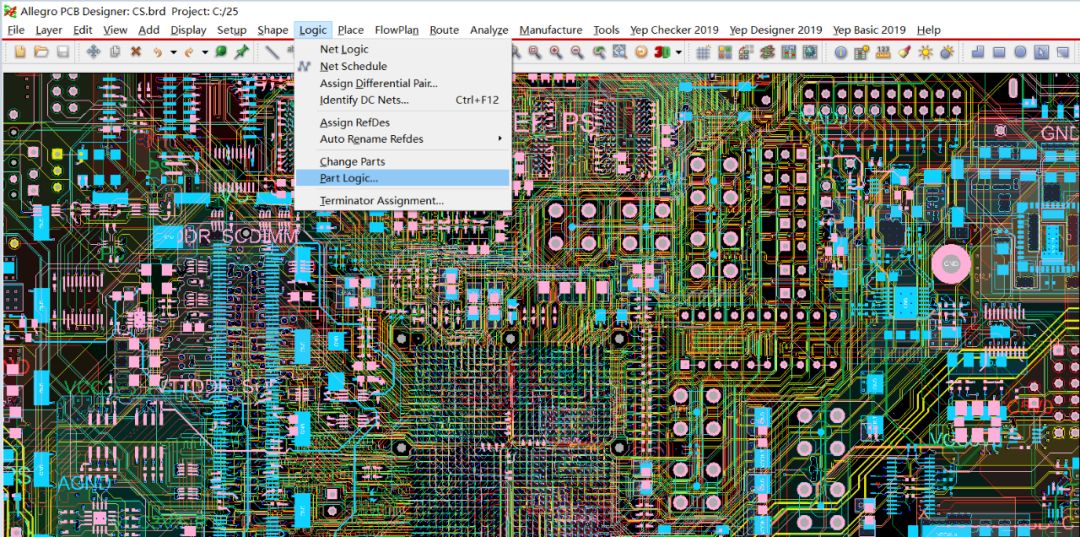

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

之前聊了《高效实现PCB自动布线的设计技巧和要点(上)》,得到不错的反响,为了能够帮助到更多的粉丝,今天来谈谈其系列的下篇。4、删除设计在删除设计阶段,要使自动布线工具能对元件引脚进行连接,表面贴装器件的每个引脚至少应有一个过孔,以便在需要

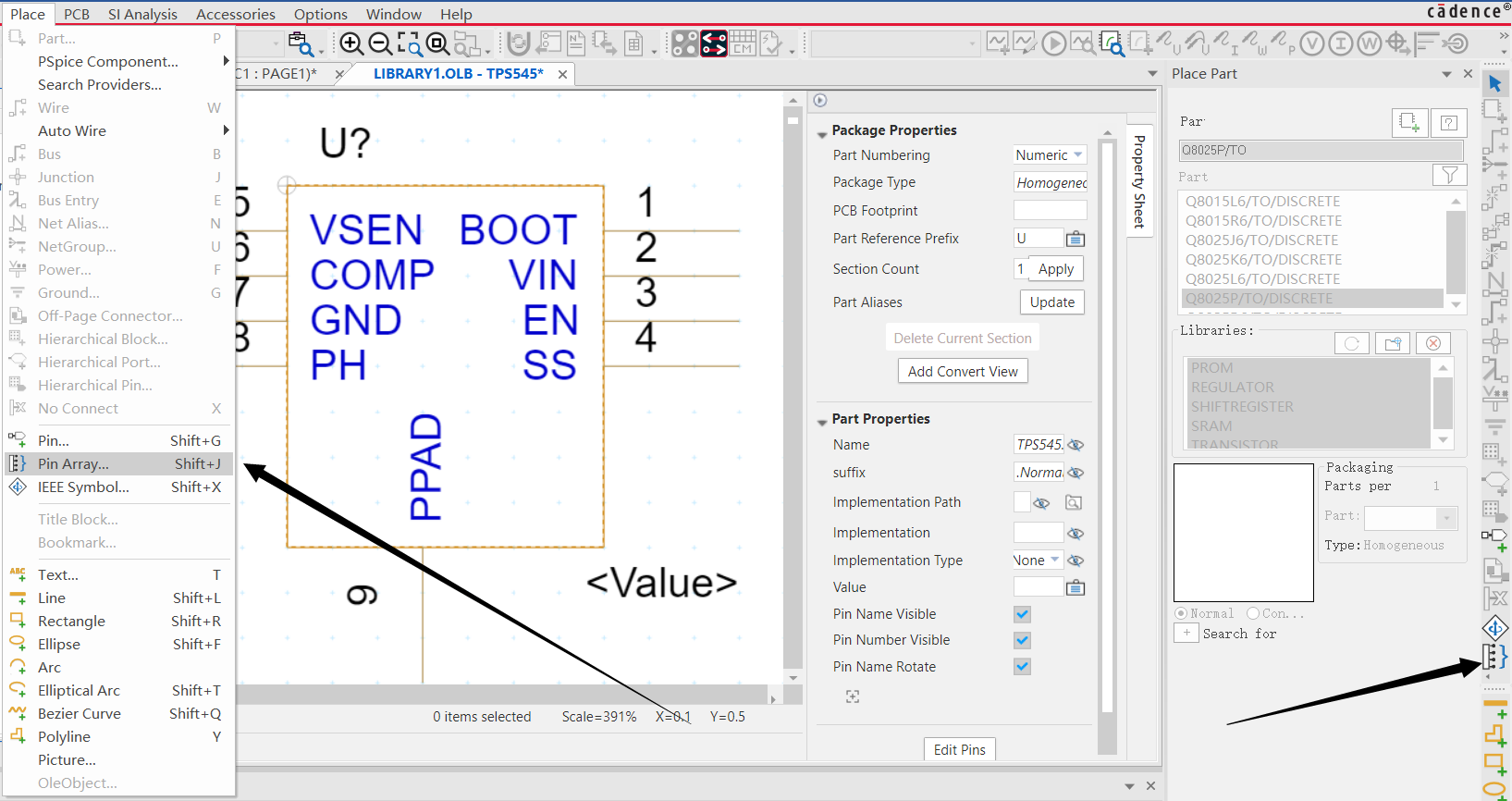

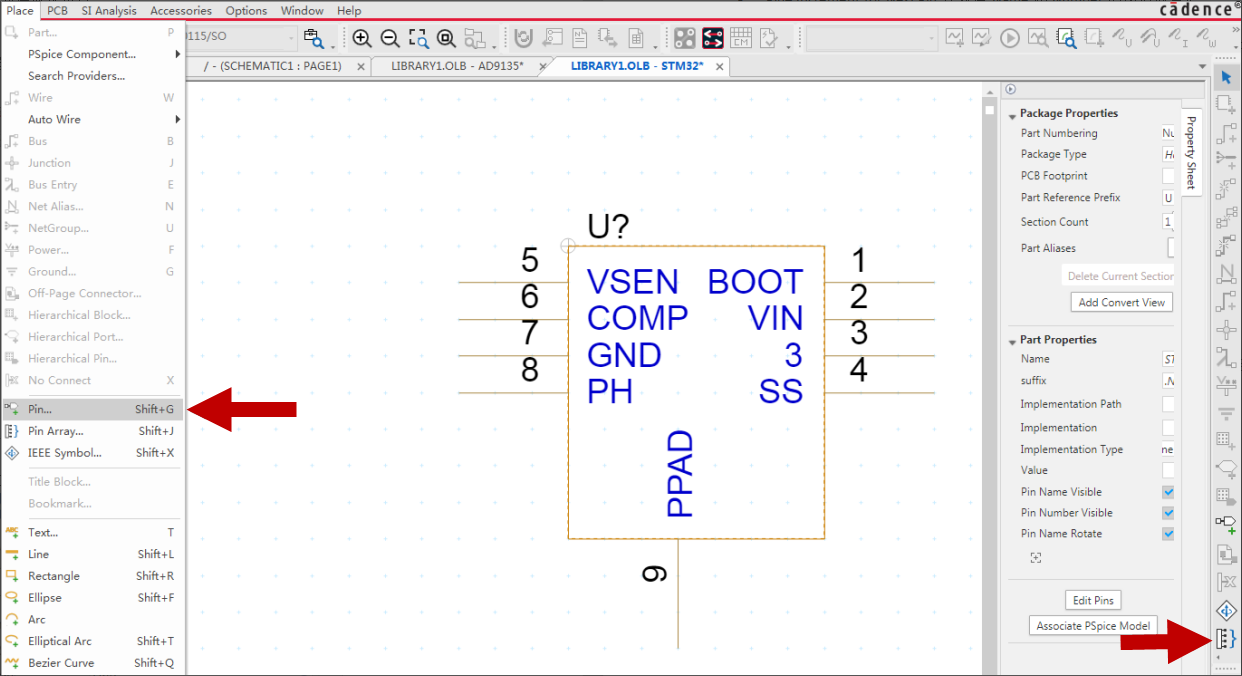

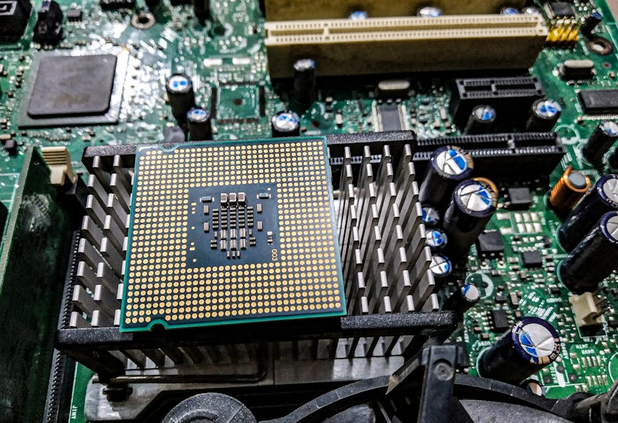

在精密而复杂的硬件设计领域,PCB封装的设计无疑是至关重要的一环。它不仅关系到元件能否顺利装配到电路板上,还直接影响到产品的整体性能与可靠性。然而,即便是经验丰富的工程师,在进行PCB封装设计时,也难免会遭遇一系列具体问题。下面一起来看看有

在PCB的可制造性(DFM)设计,会遇见各种各样的问题,其中之一是元件引脚之间有锡桥,导致电路板的性能和可靠想大大下降,若是不及时解决会产生什么影响?如何解决?1、引脚之间有锡桥,有哪些危害?短路故障:引脚间锡桥直接导致电路短路,使得电路板

扫码关注

扫码关注