- 全部

- 默认排序

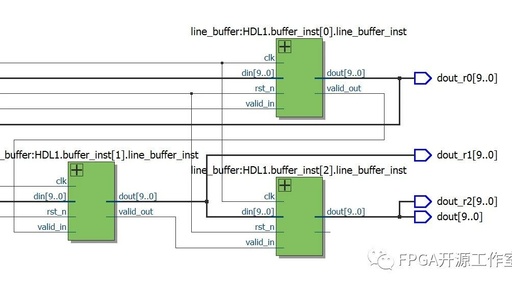

FPGA图像处理之行缓存(linebuffer)的设计二作者:OpenS_Lee01背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。0

相信对于电源工程师,示波器的功劳是不可替代的,一旦产品有问题就需要抓波形,抓时序,测试准确数值,以帮助工程师分析,处理,一切看波形说话。如何使测试的数据准确和可靠是非常重要的,准确的数字能够帮助我们,而失真的波形和数值只能误导我们。本人从事电源行业有多年,示波器就相当于我的左右手。我常常看到很多小公

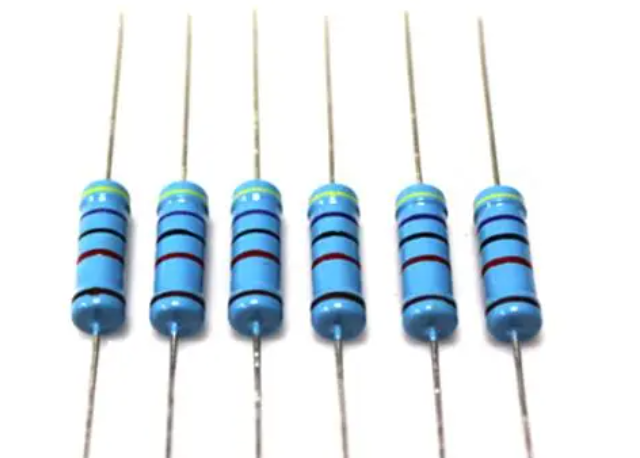

电阻是电路中常用的元件之一,而电阻的大小通常以电阻值来表示。在电阻上通常会有一些彩色的环,这些彩色的环被称为电阻色环。电阻色环的颜色和位置可以用来表示电阻的值和精度。本文将介绍如何读取电阻色环并识别电阻值。电阻色环的基本知识电阻的大小通常由

众所周知,中国自从在2005年以来成为全球最大芯片消费市场,是全球半导体市场的重要组成部分,尤其是在2021年达到峰值1773亿美元立于不败之地。但这个状况可能即将改变。近日,知名市场调研机构TechInsights预测,2023年中国芯片

提起电感线圈Q值,很多电子工程师不会陌生,电感线圈Q值是衡量其性能的重要指标,而高Q值意味着电感线圈在工作中更好地储存和释放能量,提高电路的效率及性能,因此,工程师要尽可能让Q值高一些,那么如何做?1、选择高质量的磁性材料选择具有高磁导率和

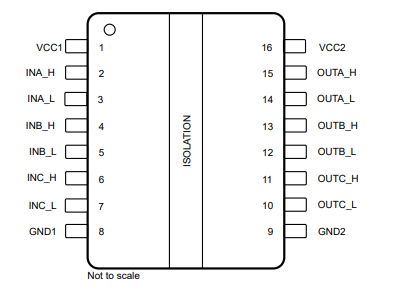

一、器件介绍ISO676x 器件是高性能六通道数字隔离器,可提供符合 UL 1577 的 5000 VRMS 隔离额定值,非常适合具有此类需求的成本敏感型应用。这些器件还通过了VDE、TUV、CSA 和 CQC 认证。在隔离 CMOS 或者

一、逻辑设计(1)组合逻辑设计下面是一些用Verilog进行组合逻辑设计时的一些注意事项:①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。②always 模块的敏感表为电平敏感信号的电路可几

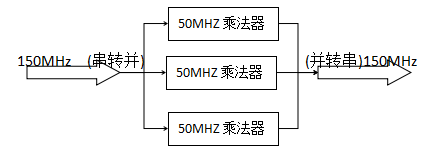

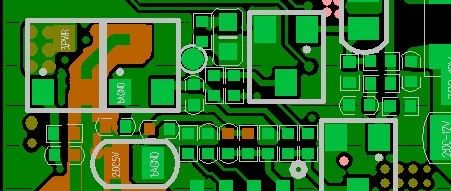

高速PCB设计指南二

高速PCB设计指南之二第一篇 高密度(HD)电路的设计 本文介绍,许多人把芯片规模的BGA封装看作是由便携式电子产品所需的空间限制的一个可行的解决方案,它同时满足这些产品更高功能与性能的要求。为便携式产品的高密度电路设计应该为装配工艺着想。 当为今天价值推动的市场开发电子产品时,性能与可靠性是

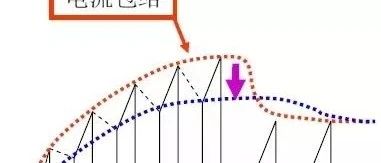

变压器饱和变压器饱和现象在高压或低压输入下开机(包含轻载,重载,容性负载),输出短路,动态负载,高温等情况下,通过变压器(和开关管)的电流呈非线性增长,当出现此现象时,电流的峰值无法预知及控制,可能导致电流过应力和因此而产生的开关管过压而损坏。变压器饱和时的电流波形容易产生饱和的情况:1)变压器感量

电源是最容易被忽视的,电源是系统运行的重要组成部分,电源就像“人体的心脏”,为系统的硬件输送血液(电),要是心脏(电源)运行不正常或供血(电)不足,会导致系统不运行或运行不稳定,在设计之前应该对核心模块峰值电流表进行知悉,供PCB Layo

扫码关注

扫码关注