- 全部

- 默认排序

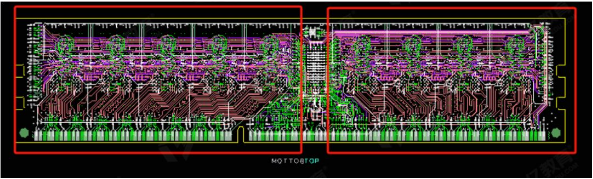

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

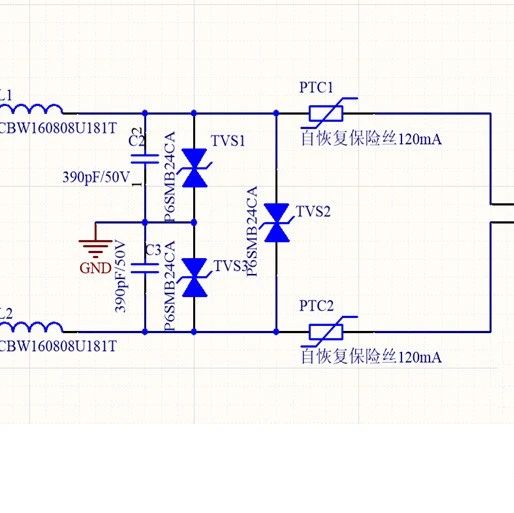

RS485电路原理图设计

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

随着电子技术的飞速发展,高速电路的传输效应已成为一个不容忽视的问题,是很多电子工程师最为头痛的问题之一。本文将详细谈谈高速电路的传输效应,并给出合理的解决方案,希望对小伙伴们有所帮助。高速电路的传输线效应是指系统工作在50MHz时,将产生传

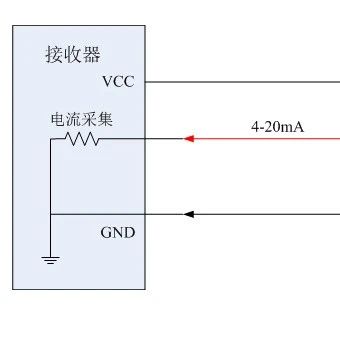

1)为什么使用4-20mA电流环在远距离、复杂的工业现场,常常需把远距离之外的信号采集回来,通常需要考虑几个问题:第一,如果直接将采集的电压信号通过长线传输,信号在传输线上会受到噪声干扰;第二,超长的导线上会有不少压降,影响传输精度;第三,如何为远端的采样电路提供电源,是个棘手的问题。为了解决上述问

在PCB设计中,走线的布局与检查是至关重要的环节。按照走线类型,可分为直角走线、差分走线及蛇形线,如何针对这三种走线方式进行高效率检查,去也报电路的稳定性和可靠性?1、直角走线容性负载:观察直角拐角处是否造成传输线上的容性负载增加,进而影响

在PCB设计中,走线的布局与检查是至关重要的环节。按照走线类型,可分为直角走线、差分走线及蛇形线,如何针对这三种走线方式进行高效率检查,去也报电路的稳定性和可靠性?1、直角走线容性负载:观察直角拐角处是否造成传输线上的容性负载增加,进而影响

在微波电子学中,PCB阻抗匹配可以确保高频微博信号高效从源点传输到负载点,避免信号的反射,进而提升整个PCB系统的能源效益,现在本文将介绍PCB阻抗匹配技术,希望对小伙伴们有所帮助。1、PCB阻抗匹配技术是什么?是指通过调整PCB上传输线的

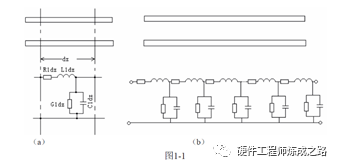

前几天写的关于示波器的文章,提到了探头上面的寄生电容,两个导体并排放置,天然就是一个电容。忽然想到,现如今HDMI 线里面的信号速率到上Ghz,HDMI线也做到了十几米,这么长,等效电容肯定不小啊?这怎么能传呢?信号不都被寄生电容滤波滤没了么?虽说这个时候也能用均匀传输线理论,集总参数模型,分布参数

在电子通信和系统设计中,信号完整性是所有电子工程师的学习重点,也是众多项目设计的重要环节,学不好信号完整性,就容易被市场淘汰,所以今天来深入理解信号完整性的关键技术参数及名词解释,希望对小伙伴们有所帮助。1、信号完整性(Signal Int

在PCB设计中,很多工程师会遇见各种问题,其中之一是差分对可以不同层走线吗?答案是可以的,这种设计策略旨在减少电磁干扰和信号损耗,特别是在高速数据传输和射频(RF)应用中。在PCB中,差分信号是一种通过两条相互耦合的传输线(即差分对)来传输

扫码关注

扫码关注