- 全部

- 默认排序

在六层及更高层的高速pcb设计中,布线的复杂性与挑战性显著增加。为确保信号完整性、电磁兼容性和整体系统性能,以下是一系列针对此类设计的具体布线策略:分层策略明确:清晰定义各层的用途,如信号层、电源层、地层等,确保信号路径最短且干扰最小化。采

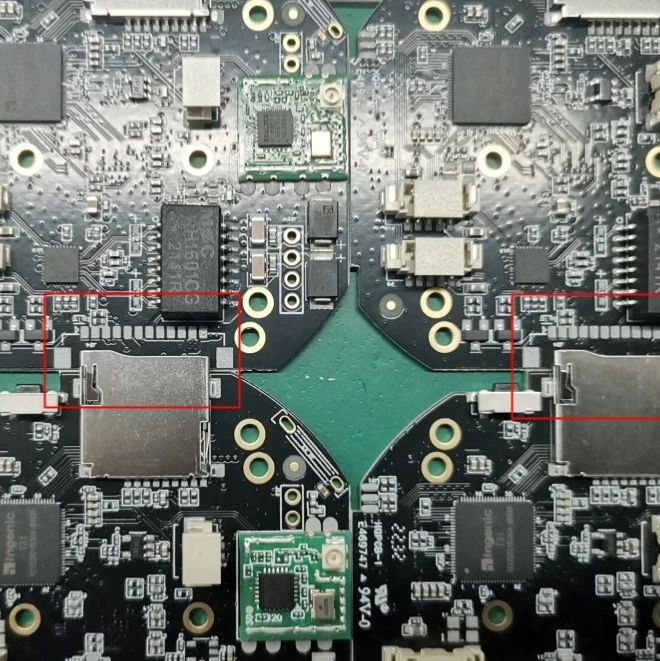

在八层高速pcb板的设计中,布线的复杂性和精度要求达到了新的高度。为了确保信号的高速传输、优异的电磁兼容性和系统的整体稳定性,以下是一系列针对八层高速pcb板布线的具体指导原则:精细分层规划:首先,明确每一层的用途,包括信号层、电源层、地层

数十年来,IPC 一直在与业内专业人士合作,制定有关 pcb 设计和制造的综合标准。在大多数情况下,这些努力都取得了成效,而且在这些标准小组的参与者中形成了一种持续改进的文化。制定标准的一个重要领域是定义 pcb 线路中的电流限制,但标准的准确性却不尽如人意。涵盖这一设计领域的两个标准是 IPC-2

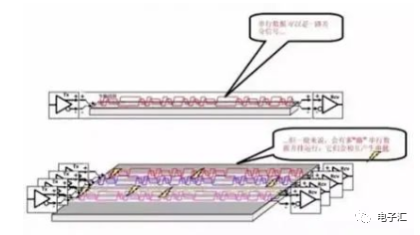

信号串扰知识讲解

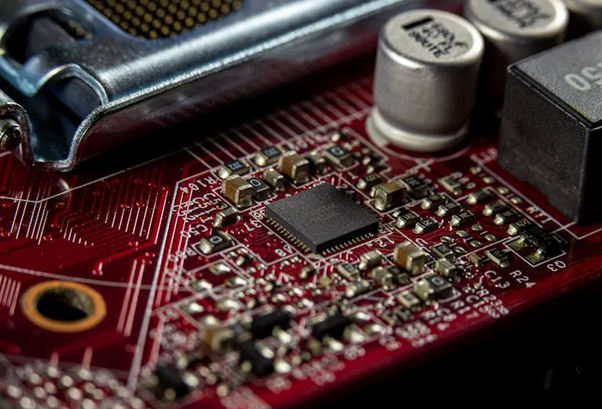

在射频电路研究学习的过程中,相信大家都遇到过在电路中信号频率的变高、边沿变陡、电路板的尺寸变小、布线的密度变大等问题,这些几乎是不可避免的问题。这种影响信号完整性的问题叫做串扰,在电路计中普遍存在,有可能出现在芯片、pcb板、连接器、芯片封装和连接器电缆等器件上。如果串扰超过一定的限度就会引起电路的

很多人说,电子工程师是一个苦逼的职业,其实哪个行业的工作没有几个不苦逼的,你看到别人拿高薪,却不知道别人背地付出的巨大努力。很多电子工程师在自己岗位上埋头苦干,时至今日也未能真正知晓电子人的核心竞争力是什么,或许屏幕前的你也不曾知晓。电子工

在信号传输中,大家都知道,线宽(即导体或传输线的横截面积)的粗细,将决定着损耗的大小,因此有人提出“只要空间允许,线宽无限大,损耗是否可以一直小到0?”这种说法是否正确?首先,这个想法虽然很美好,但却是错误!在理想情况下,随着线宽的增加,单

在半导体技术日新月异的今天,封装技术作为链接芯片与外部世界的桥梁,其重要性不言而喻。其中,CSP(Chip Scale Package)封装技术以其极致的小型化特性,成为追求高性能、轻薄化电子产品的首选方案。本文将简短介绍CSP,希望对小伙

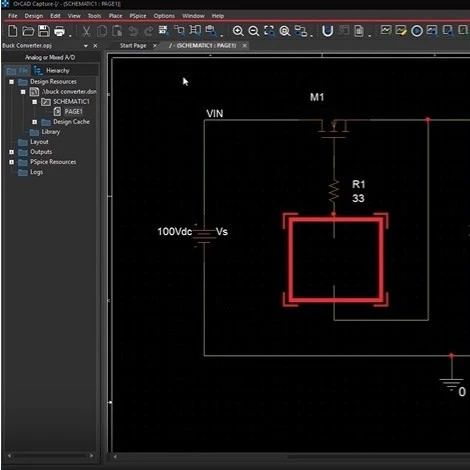

关键 要点电路仿真软件和 pcb 设计软件在 pcb 设计过程中发挥着互补作用,为工程师提供设计、仿真、验证和优化电子电路的工具。有效的仿真分析有助于减少开发所需的设计、制造和测试迭代次数,确保电路设计在板制造前满足性能和操作目标。PSpice 仿真工具和 OrCAD X pcb设计软件是Cad

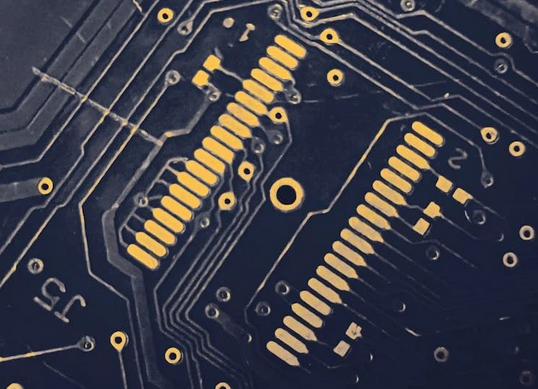

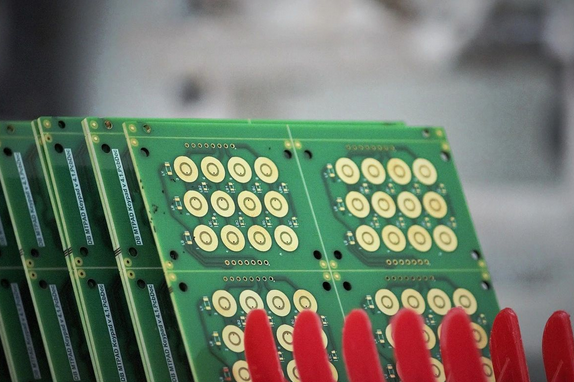

pcb的拼版是一个至关重要的环节,它不仅影响着产品的生产效率,也直接关系到产品的质量和成本。合理的拼版能够优化生产流程,减少浪费,提高产能。然而,在实际操作中,由于各种因素的影响,很多工程师的pcb拼版存在着不少问题。本文将带您探讨pcb拼版的合理性与重要性,帮助您深入了解如何优化拼版设计,提高生产

许多电子工程师会选择Cadence Allegro来设计pcb,在使用时会遇到许多操作,其中之一是在Cadence环境中创建封装库,确保数据的高效与准确,那么在操作Cadence时需要注意什么?1、精确测量与缩放Pad尺寸根据Pin脚的精确

扫码关注

扫码关注