- 全部

- 默认排序

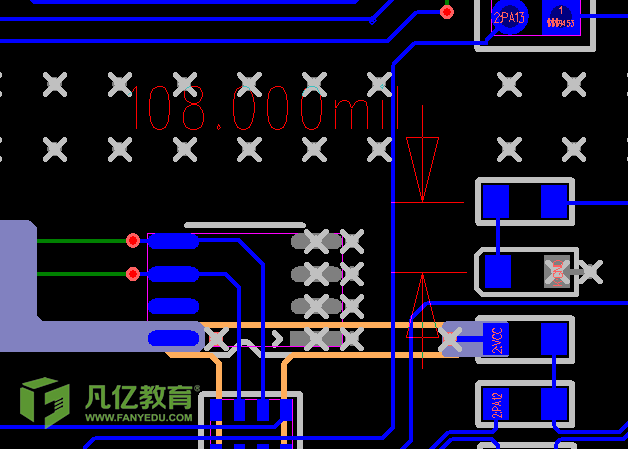

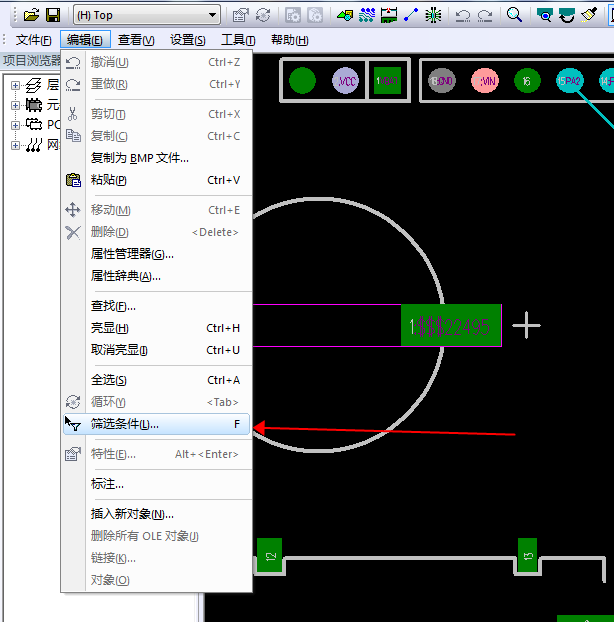

在layout中布局时,经常需要测量间距,有时候会发现测量的间距有误差并且我们在layout中出cam文件时,有时会弹出钻孔精度报错,其实都是因为我们的测量精度设置有误

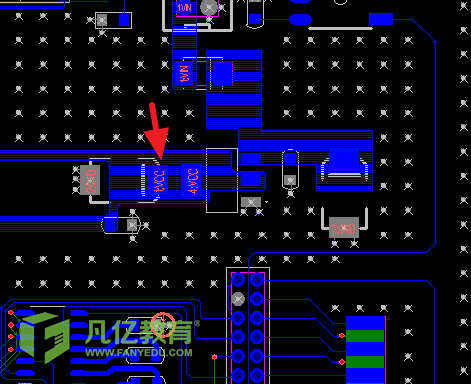

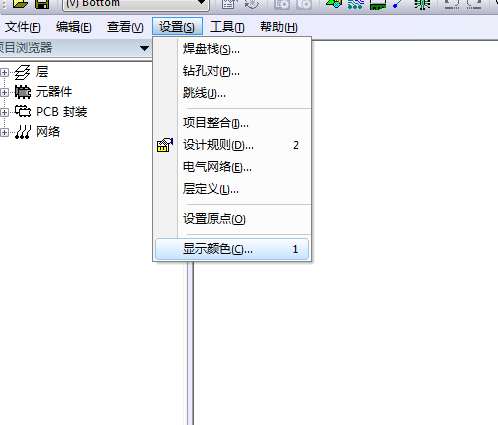

我们在进行pcb设计时,为了提高设计的效率,需要为一些特定的网络设置颜色这样可以在布线时更好的分便,那么怎在layout中设置网络的颜色呢

FPGA(现场可编程门阵列)自诞生以来就一直在冲击着专用集成电路(ASIC,Application Specific Integrated Circuit)芯片界的神经。在20世纪80年代中期,RossFreeman和他的同事从Zilog手中购买了这项技术,并着手创办了针对ASIC仿真和教育市场的Xilinx。(Zilog出自埃克森美孚石油公司,因为在20世纪70年代,人们已经开始担心石油会在30年后枯竭,这一点在今天仍然适用)。同时,Altera也以类似的技术为核心成立。 FPGA是由电路编程

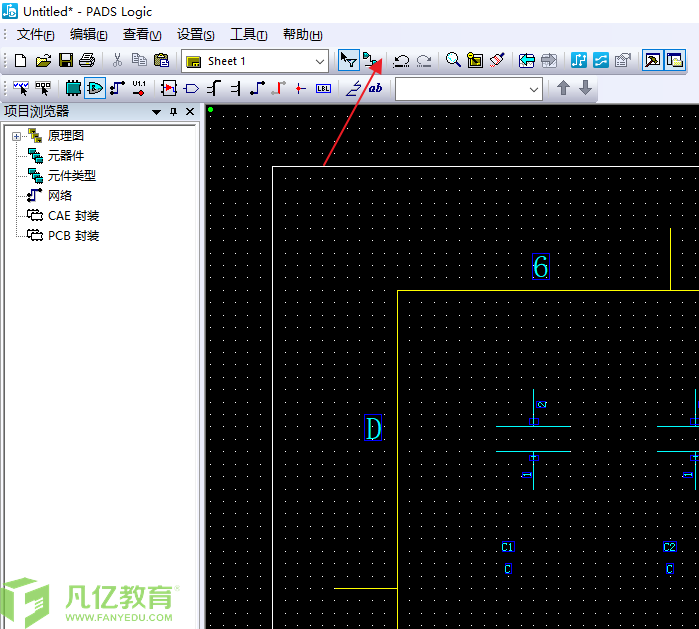

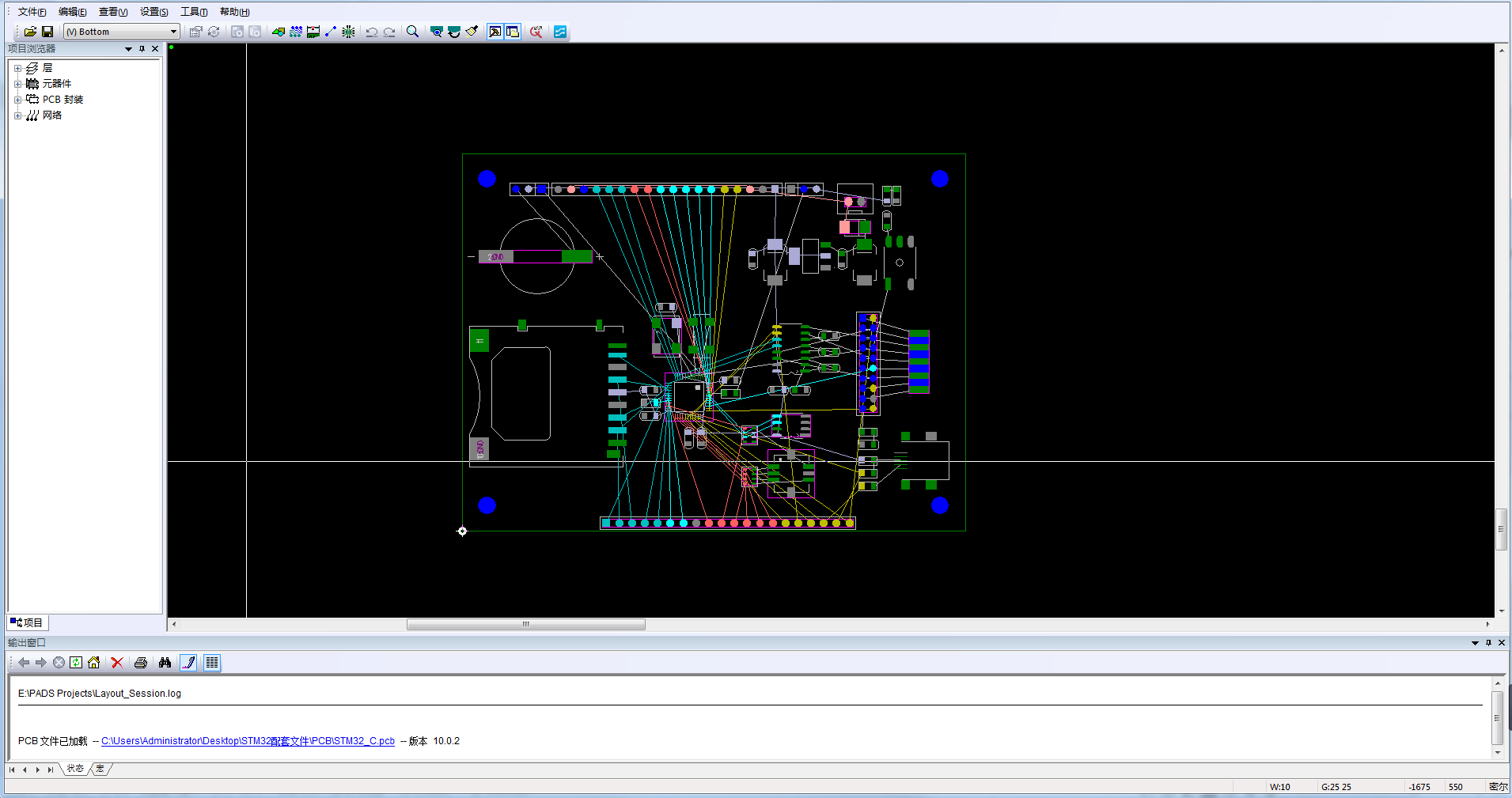

Pads Layout中的用户界面与我们的Pads Logic的用户界面是十分的相似,以致于许多人在这两者之间分不清楚。那我们的Pads Layout用户界面是由标题栏,设计工作区域,菜单栏,状态栏和输出窗口这几部分组成

在我们进行Pcb设计的时候,需要对于实际的pcb走线布局等进行规则设置,那么Pads Layout提供了多种设计的规则,如设置默认的安全间距,布线规则和网络规则等。

pads简介及设计流程

对于PAds及其发展历史,有兴趣了解的可以上网搜一下,这里我们就简单介绍一下PAds的用途以及我们使用到的PAds组件。PAds是用来设计原理图和PCB的专业软件,功能十分强大,尤其是在多层板的设计上。这里我们不和其它同类软件做比较,每个软件都有自己的有点,全看自己的爱好和工作环境。在具体的设计过程中,主要使用到PAds的3个组件,分别为:PAds Logic、PAds Layout、PAds Router;PAds Logic:用来设计原理图,同时原理图库和库中的元器件也需要在PAds Log

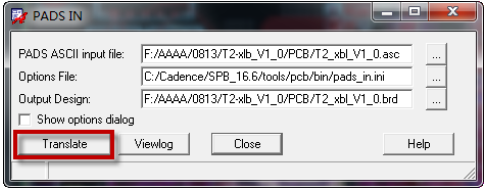

Pads封装导入到Allegro,一般先是通过Pads PCB转Allegro PCB,转换完成后,将封装导出,再逐个对PCB封装进行检查修改,修改为标准可用的封装。

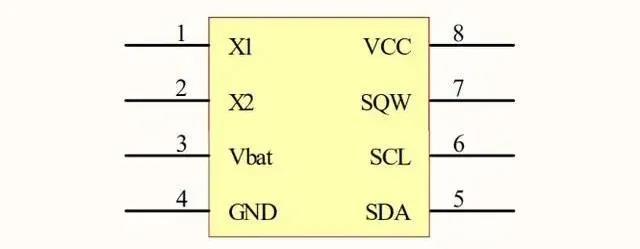

工程师在开发一个电路系统,往往会需要用到中央处理器,比如单片机、FPGA、或者dsP等等;当然一些简单的纯硬件电路项目方案例外,如充电器、热水壶等等。 作为单片机研发设计的项目,它的最小电路工作系统包含电源电路、复位电路、时钟频率电路;其中电源电路与复位电路,相信工程师都非常容易理解与设计。然而时钟频率电路,由于不同的开发项目功能需求不一样,设计的方案选择也不尽相同,很难得到有效的统一设计。

扫码关注

扫码关注