- 全部

- 默认排序

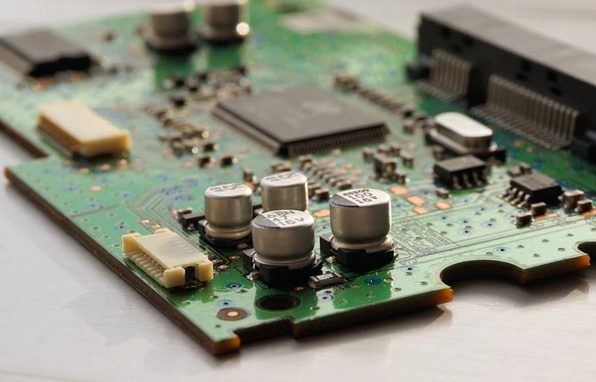

电子工程师,第一次接触多层PCB板时,动辄十层八层的,线路像蜘蛛网一样,密密麻麻的,很容易看晕。甚至相比单双面板,多层板的设计难度是随着层数的增加,翻倍增长。8层PCB板的基本结构是由6个内部层和2个外部层组成,每一层都有其独特的功能,比如

在数字电路设计与开发过程中,debug是确保电路功能正常、系统稳定运行的关键步骤,可以帮助工程师快速定位解决问题,如果不能很好解决debug列出的问题,很容易导致电路有一定问题。1、检查电源确认电源电压:确保所有电源电压均达到设计规格,包括

Wi-Fi(Wireless Fidelity)作为现代无线通信的重要技术之一,广泛应用于家庭、办公室及公共场所。为了确保多个设备在共享无线信道时能够高效、有序地传输数据,Wi-Fi采用了一套复杂的机制,其中载波监听与冲突避让机制是关键所在

在计算机系统中,数据的存储方式有很多种,其中大小端模式(Big-endian和Little-endian)很常见,它们决定了多字节数据在内存中的排列顺序。1、大小端模式是什么?①大端模式(Big-endian)数据的高位(High-orde

串行调试(Serial Wire debug,简称SWD)是一种调试协议及对应的硬件接口,也是一种用于微控制器和其他嵌入式系统的调试接口,与JTAG接口相比,SWD接口具有引脚数量少、结构简单的特点。1、SWD接口的引脚数量JTAGV6/J

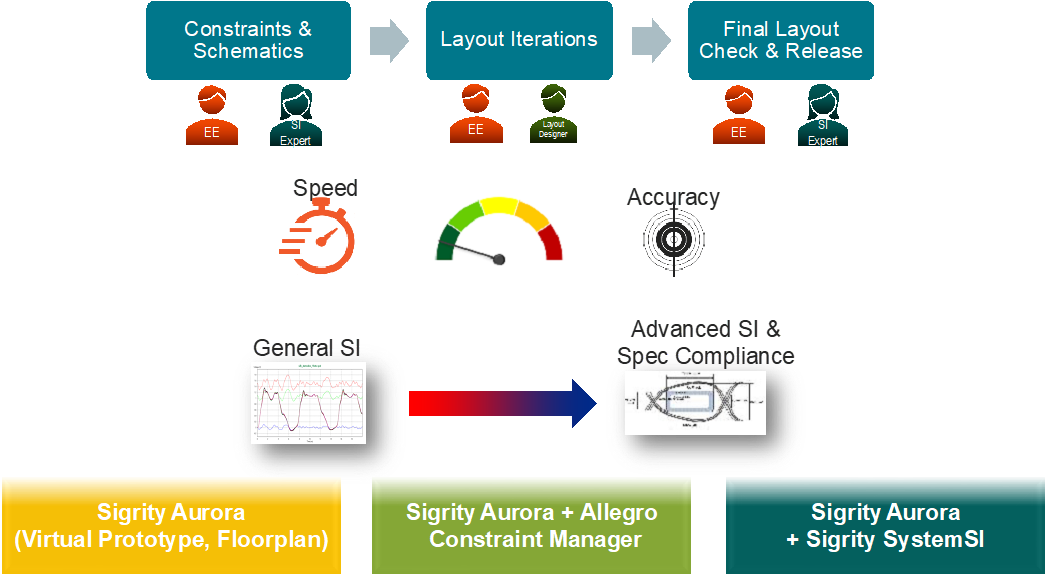

本文作者为 Cadence design Systems 产品管理组总监 Brad Griffin,文章首发于 iconnect007.com。预计阅读时长:18分钟本文将重点介绍如何在无需久等 SI 和 PI 专家反馈的情况下,助力 PCB 设计团队在预算范围内按时交付合格的产品。对于当今设计高速

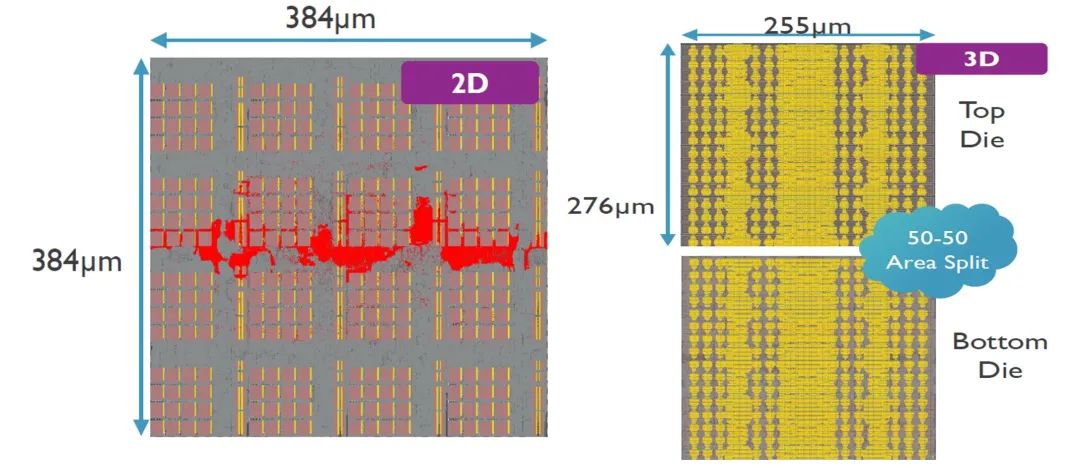

Cadence员工Mohamed Naeim 博士曾在CadenceLIVE 欧洲用户大会上做过一场题为《2D/3D 热分析和三裸片堆叠设计实现》的演讲,本文将详细讲述该演讲内容。实验:两个裸片是否优于一个裸片?由于线长缩短,3D-IC 会减少功耗,带来性能提升。在此,3D-IC 指的是将一个裸片(

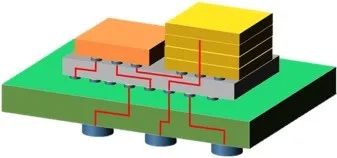

在今年的 IMAPS(International Microelectronics Assembly and Packaging Society,国际微电子装配与封装学会 )大会上,Cadence 资深半导体封装管理总监 John Park 发表了关于封装组装设计套件(Package Assemb

电子管是一种使用真空或者气体环境中电子输运现象的通用术语。主要分为热电子管、冷阴极管、热阴极管和特种电子管等多种类型。其中,最常见的是真空电子管,如三极管、二极管、真空管等。晶体管是一种半导体器件。它是在1947年由Bardeen、Brat

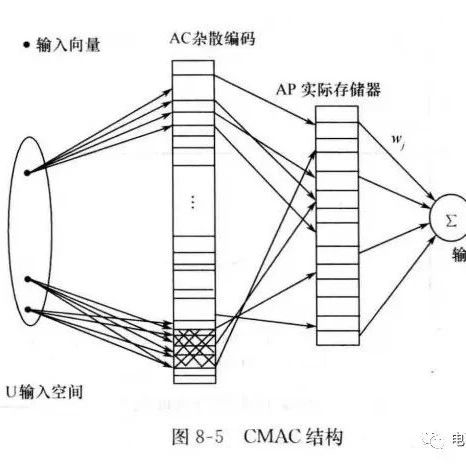

1 CMAC概述小脑模型神经网络(Cerebellar Model Articulation Controller,CMAC)是一种表达复杂非线性函数的表格查询型自适应神经网络,该网络可通过学习算法改变表格的内容,具有信息分类存储的能力。CMAC把系统的输入状态作为一个指针,把相关信息分布式地存人一

扫码关注

扫码关注