- 全部

- 默认排序

答:我们在进行差分布线设计的时候,特别是高速信号差分,在进行打孔换层的时候,都会在旁边添加回流地过孔,若差分信号比较多的时候,去添加,就非常繁琐,也容易遗漏,我么这里讲解一下,如何去进行自动添加,具体操作如下所示:

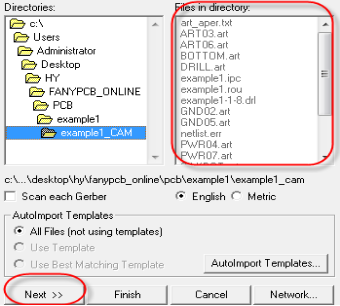

答:第一步,打开Cam350软件,点击File-Import-AutoImport选项,如图6-322所示;

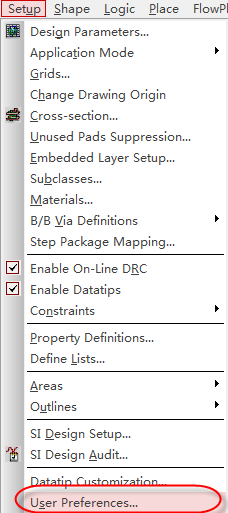

答:第一步,点击Setup-User Preferences选项,如图6-325所示;

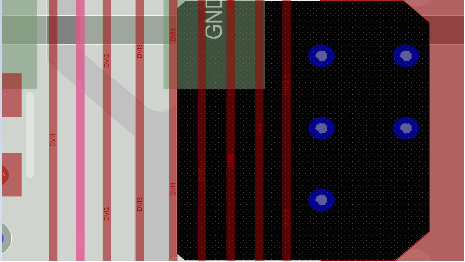

答:做PCB设计时,有些区域可以设置禁止铺铜,但是允许走线。第一步,点击Setup-Areas-Shape Keepout,在需要禁止铺铜的区域画好禁示区域,如图6-327所示;

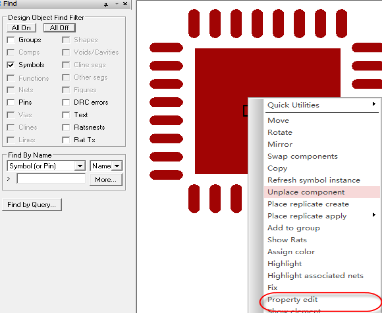

答:使用Allegro进行PCB设计时,一般我们不能将一个封装里的焊盘管脚单独移动,通常是整个封装一齐移动。如若需要将焊盘单独移动,可按以下步骤处理:

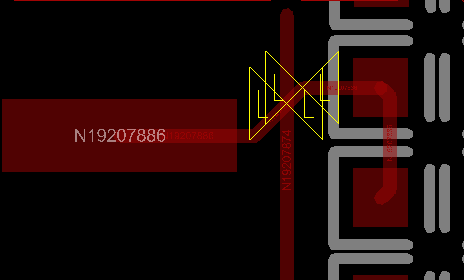

答:在使用动态铜皮的时候,会出现对铜皮进行Update to Smooth完了,还存在Out of date shapes的现象,如图6-332所示:

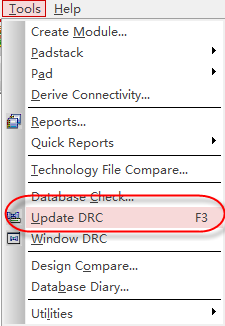

答:使用allegro软件进行PCB设计,一般会使用约束规则辅助设计,当设计时有对象违反了设置的约束规则,软件会以DRC标记的形式提醒设计者。

答:我们PCB布局完成之后,需要对网络进行扇出,一般空的管脚、空的网络不需要进行扇出,为了提高布线效率,我们会对空的网络进行高亮显示,具体的操作步骤如下所示:

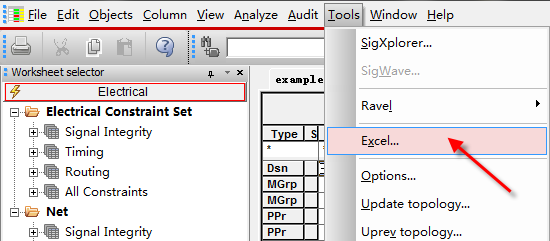

答:我们在进行完PCB设计完成,在规则管理器中是有等长数据的,如图6-355所示,这样可以清晰的反馈等长的数据,这样去看是非常直观的。这是在电脑中安装了allegro软件的情况,如果没有软件,就没办法查看参数了,所以,我们这里讲解一下,如何导出Excel表格的等长数据表,具体操作步骤如下所示:

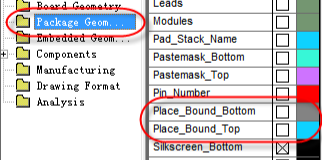

答:我们在进行PCB设计时,遇到比较复杂的结构,会有一些限高的区域以及禁止布器件的区域,所以我们需要知道PCB元器件的高度信息,这里讲解下,在PCB中如何去查看元器件的高度信息,具体操作步骤如下所示:

扫码关注

扫码关注