- 全部

- 默认排序

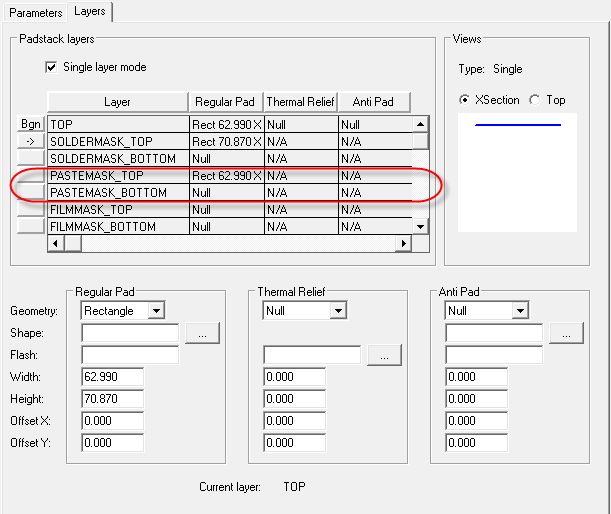

答:1)钢网大小应该与焊盘是一样大的; 2)贴片焊盘才会有钢网,插件是不需要做钢网的; 3)为保证足够的锡浆/胶水量及保证焊接质量,常用推荐钢片厚度为: 印胶网为0.18mm-0.2mm, 印锡网为0.1mm-0.15mm; 4)为保证钢网有足够的张力和良好的平整度,通常建议钢片边缘距网框 内侧保留有20~30mm;5)我们在allegro软件中设计焊盘的钢网,需要用到焊盘编辑器,也就是Pad

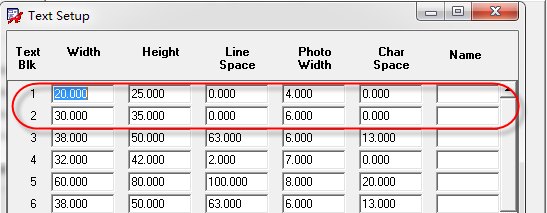

常规设计中,方便后期PCB板查看位号,一般采用如下设置,字粗(Photo Width)/字高(Height)/字宽(Width)的比例为:Ø 常规的PCB板卡设计,为:5/30/25mil;Ø PCB板卡密度较小,为:6/45/35mil;Ø PCB板卡密度较大、或者局部过密,为:4/25/20mil。在allegro软件设计中,只需要更改text字号的大小即可,一般推荐2号字为常规设计,1号字为偏小设计,如图1-29所示。 图1-29 PCB

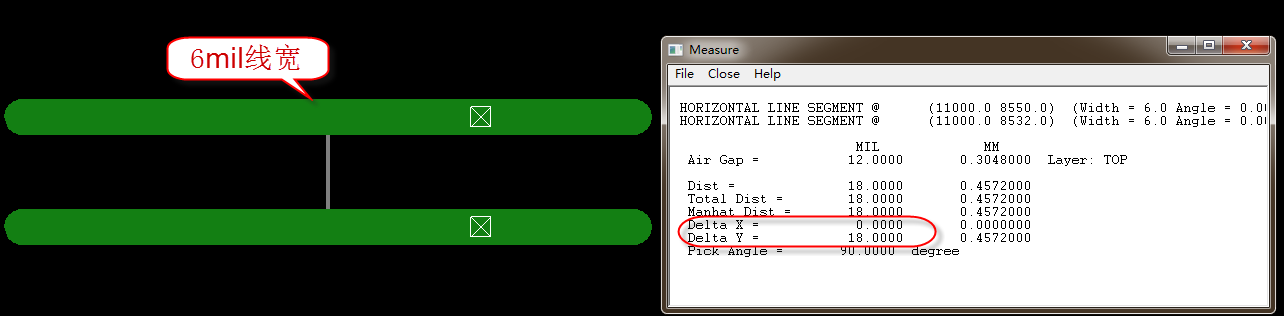

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

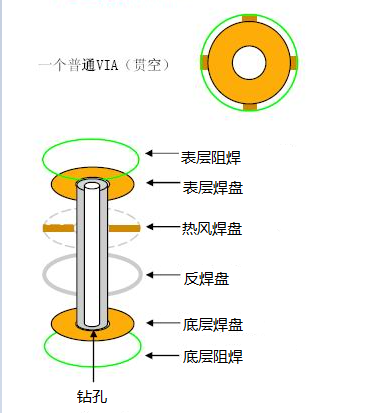

答:过孔,也叫金属化孔。在双面板和多层板中,为连通各层之间的印制导线,在各层需要连通的导线的交汇处钻上一个公共孔,即过孔。过孔的实质呢,其实就是一个通孔的焊盘,有外径和内径,我们可以从图1-48所示的过孔的padstack剖析图来看下,通孔的焊盘在allegro软件中所包含的元素。 图1-48 通孔焊盘剖析图Regular Pad:规则焊盘,在正片中看到的焊盘,也是基本的焊盘。Thermal Relief:热风焊盘,也叫花焊盘,在负片中有效,设计用于在负片中焊盘与敷铜的接连方式,防止焊

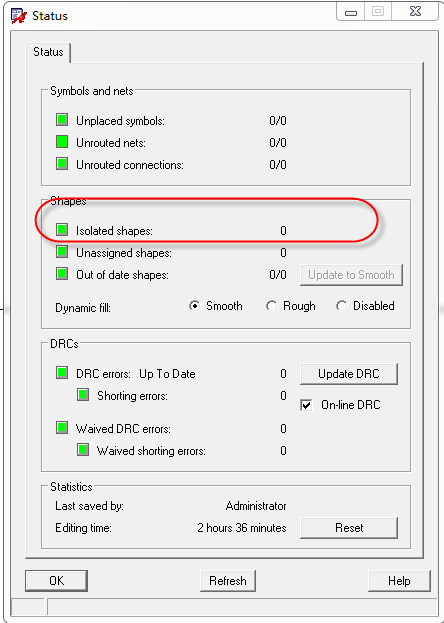

答:孤岛铜皮, Isolated Shapes,也叫做孤岛,指的是在PCB中孤立、没有与任何地方连接的铜箔。在allegro软件中,系统会自动统计孤岛铜皮的个数,如图1-49所示,对于PCB板上的孤岛铜皮,一般我们在设计的时候,对于很大块的孤岛铜皮,我们尽量在这个铜皮打上地过孔。让铜皮接地,使整个PCB地连接性更好;而对于面积很小的孤岛铜皮,我们选择删除,点击shape-Delete Island,就可以把整个孤岛铜皮给删除掉,如如1-50所示。孤岛铜皮的存在,主要是会与周

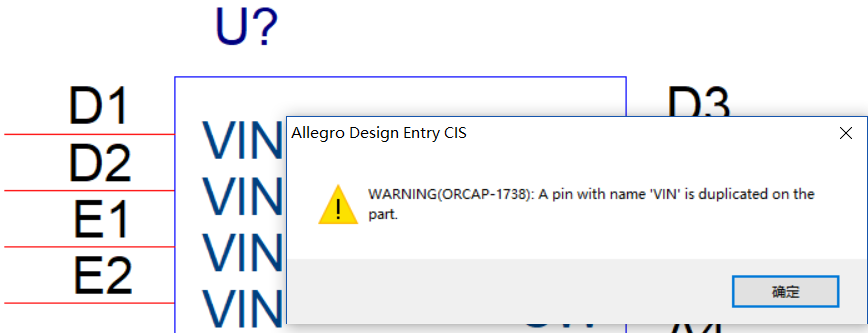

答:在绘制原理图库,会出现一些管脚名称是一样的,一般是电源管脚或者是空管脚,当名称重复的时候,保存原理图库的时候,会弹出如图2-78所示的警告,提示有重复的名称,后面输出allegro网表的时候,会报错。对于这种情况,我们做如下处理: 图2-78 原理图库管脚名称相同警告示意图Ø 电源管脚名称一致的,我们将电源管脚的属性改为power属性,这样系统就会允许管脚名称是一致的,不会报警告,如图2-79所示; 图2-79 电源管脚属性示意图Ø

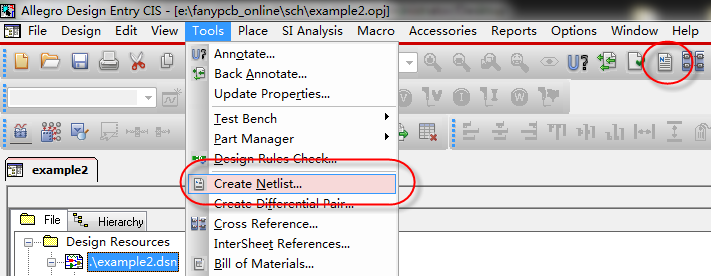

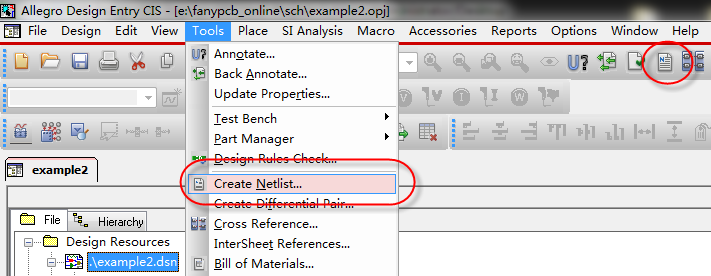

答:orcad产生Cadence allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生allegro的第一方网表,如图3-69所示; 图3-69 allegro第一方网表参数设置示意图第三步,输入allegro第一方网表需要注意下面几个

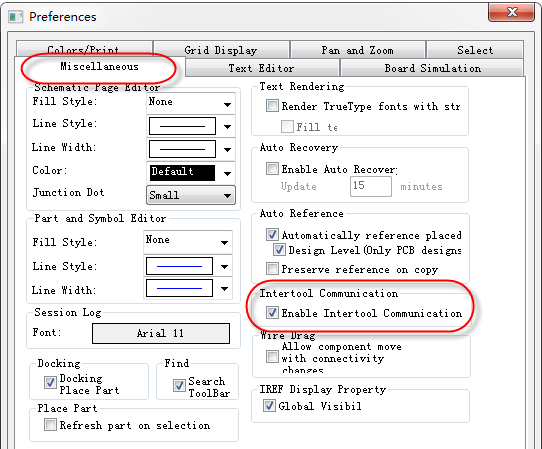

答:orcad与Cadence allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是allegro的第一方的网表,allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

答:使用Orcad软件进行输出allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足allegro软件的要求,不能输出网表, 图3-72 输出allegro网表报错示意图在输出allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:orcad产生Cadence allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

扫码关注

扫码关注