- 全部

- 默认排序

ADM2582E/ADM2587E是具备±15 kV ESD保护功能的完全集成式隔离数据收发器,适合用于多点传输线路上的高速通信应用。其内部集成的RS-485驱动器带有一个高电平有效使能电路。

外媒报道称,总部位于布鲁塞尔的化学公司索尔维和法国AubervillieRS的威立雅宣布成立循环经济联盟,旨在提供新的解决方案来提高汽动力电池中金属的资源利用效率。

Lucid Air号称充电速度最快的电动汽车,充电一分钟增加20英里续航-据国外媒体报道,当地时间周三,美国电动汽车初创公司Lucid MotoRS宣布,Lucid Air将是有史以来充电速度最快的电动汽车,每充电一分钟可以为汽车增加20英里(32.19公里)的续航里程,相当于在真实环境下充电20分钟可恢复300英里(约合482.8公里)的续航。

Lucid Air号称充电速度最快的电动汽车,充电一分钟增加20英里续航-据国外媒体报道,当地时间周三,美国电动汽车初创公司Lucid MotoRS宣布,Lucid Air将是有史以来充电速度最快的电动汽车,每充电一分钟可以为汽车增加20英里(32.19公里)的续航里程,相当于在真实环境下充电20分钟可恢复300英里(约合482.8公里)的续航。

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:执行菜单命令Options→Preference,弹出如图2-5所示界面,在此界面中选择ColoRS/Print选项,进行颜色跟打印设置选项,每一个颜色设置前面都一个勾选的选项,勾选表示的含义是打印这份原理图的时候,这个参数显示在打印的图纸上,反之不显示在图纸上。 图2-5 颜色设置示意图如果需要修改颜色,直接鼠标左键单击相对应的颜色框进行修改就可以了,右下角是系统默认颜色,点击下就恢复到系统默认的颜色。下面对几个常用的参数进行说明如下:Ø Alias:网络标

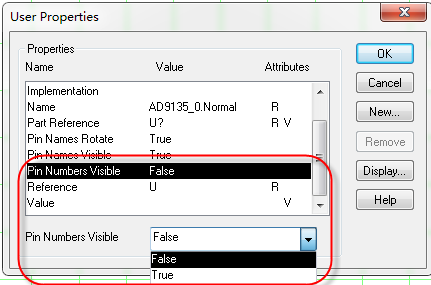

答:在设计的时候,有一些原理图符号不需要将管脚编号显示,比如电阻、电容、二极管等元器件,我们的操作方法如下:第一步,打开所要隐藏管脚编号的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中选中Pin NumbeRS Visble,修改Value值属性即可;第三步,需要显示管脚编号的,Value值那一栏选择True;隐藏管脚编号的,Value值那一栏选择False,如图2-48所示: 图2-48 隐藏与显示管脚编号示意图

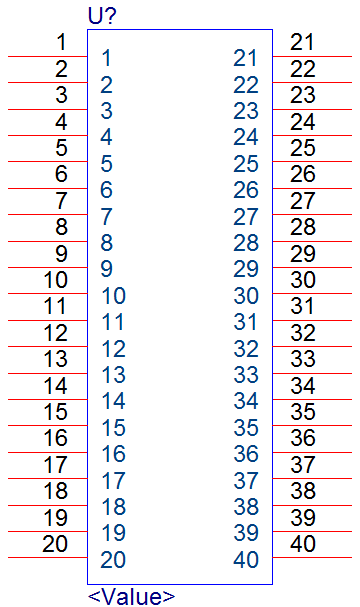

答:针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改,操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称Name以及管脚编号NumbeRS先按数字1、2、3...,一致往下排,如图2-64所示; 图2-64编辑管脚属性示意图第二步,用鼠标左键框选所有的管脚,点击右键,Edit Properties…,编辑属性,如图2-64所示;第三步,在弹出的界面中进行对应参数的设置即可,如图2-65所示,可以运

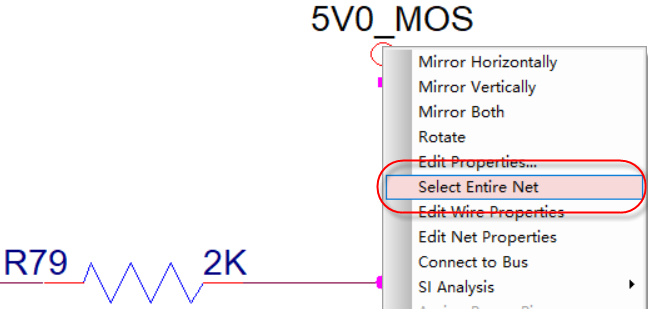

答:第一步,打开任意一页原理图,单击左键选中一个网络,然后单击鼠标右键,选择Select Entire Net,进行网络点亮,如图3-40所示: 图3-40 网络高亮设置示意图第二步,选择Select Entire Net以后,回到原理图的界面,可以看到所有的这个网络的连线都显示高亮的颜色,如图3-41所示; 图3-41 网络高亮显示示意图第三步,为了方便查看,高亮的颜色即选中的颜色是可以更改的,执行Options→Preferences…菜单,选择ColoRS即可进行更改,

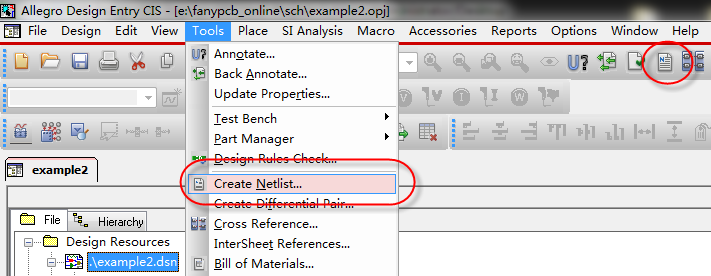

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在FormatteRS栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

扫码关注

扫码关注