- 全部

- 默认排序

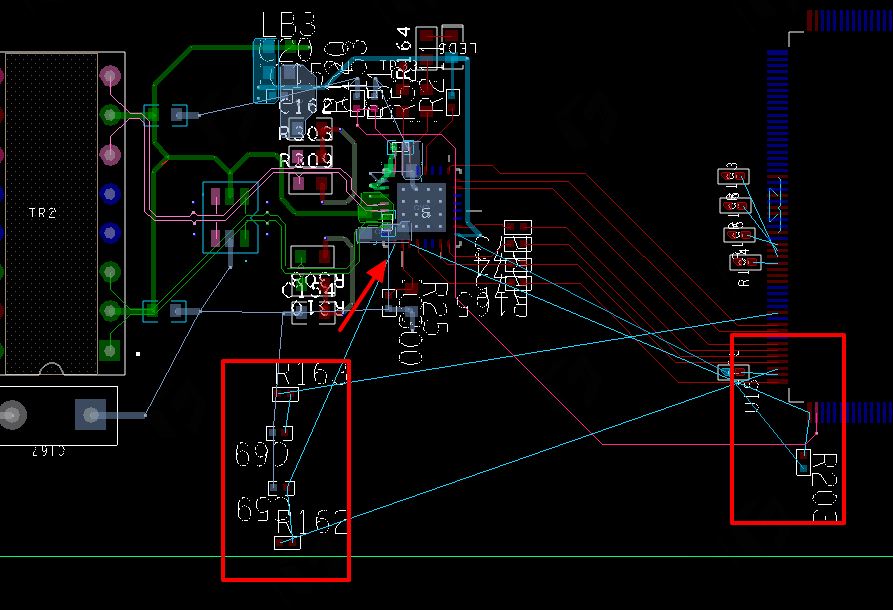

1.布局、布线未完成,多处电源信号、时钟信号等重要信号未布局。2.差分对内等长错误3.内层负片没有铜皮,地和电源网络都没有连接4.以太网芯片到CPU的GMII接口线的发送部分需要等长,建立rx、tx分别等长控制100mil误差范围以上评审报

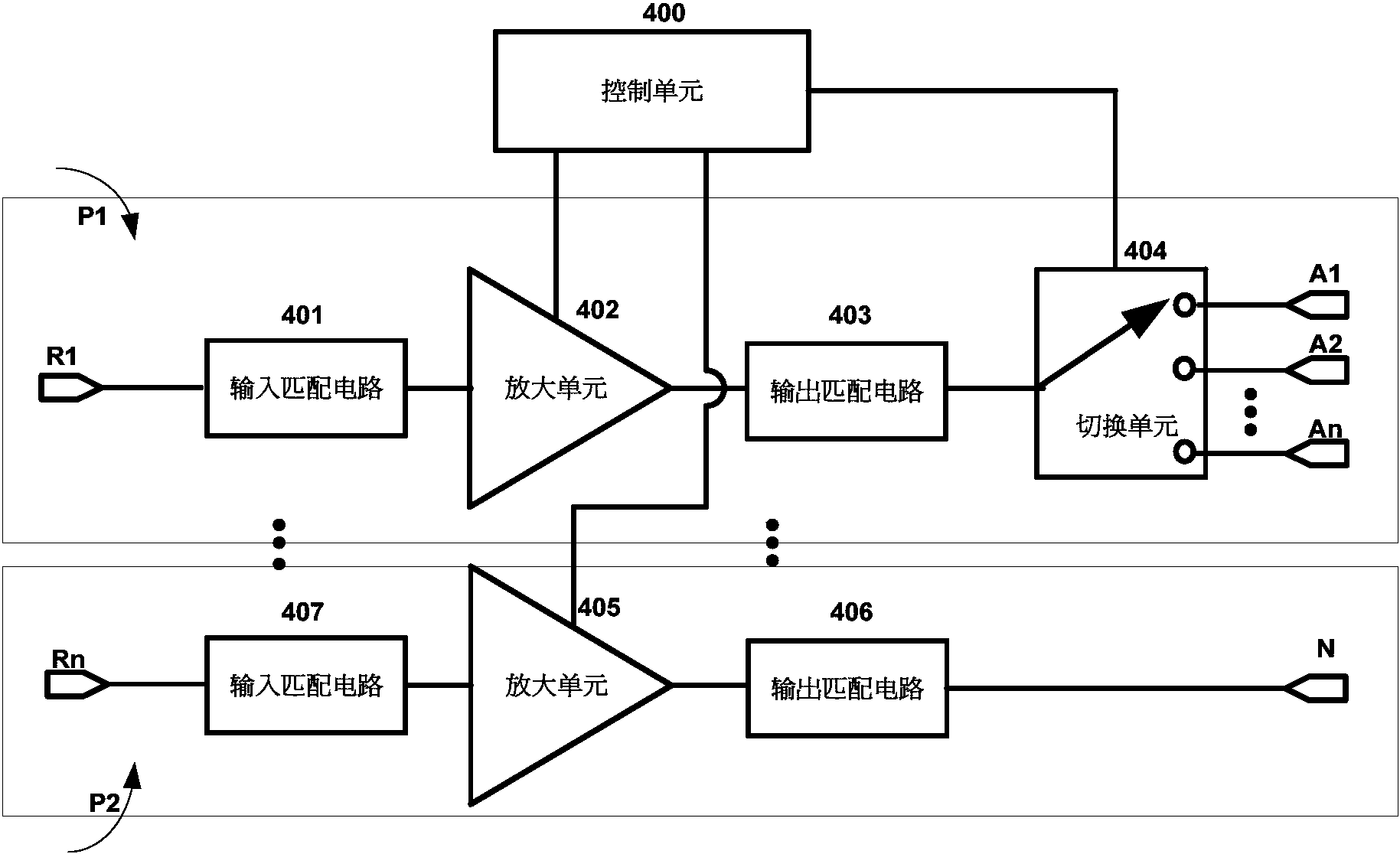

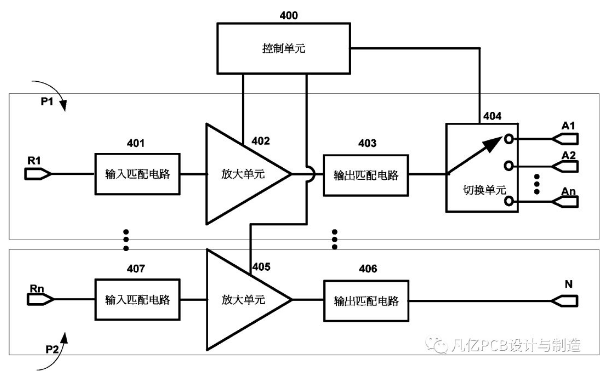

射频(Radio FrequeNCy,RF)电路在现代电子领域中扮演着至关重要的角色,涵盖了广泛的应用,从通信系统到雷达和射频识别(RFID)等。在高速PCB设计中,射频电路的分析和处理是一项具有挑战性的任务。本文将介绍高速PCB设计中常见

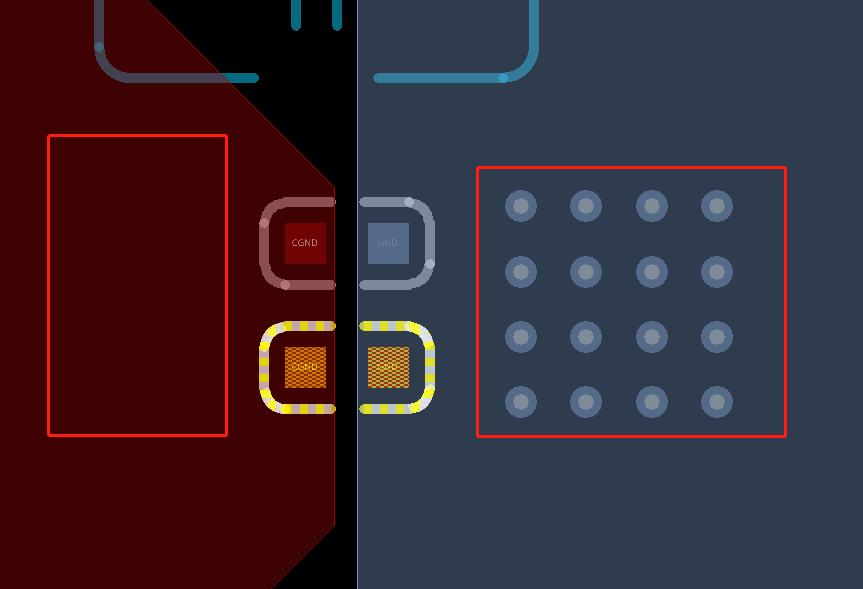

跨接器件的地过孔打在地焊盘旁边,如右侧的电路地打孔一样:注意变压器上除了差分信号,其他的信号走线20MIL:注意走线规范,不要从电阻电容内部穿线,更改此信号的路径:注意扇孔间距保持,不要吧负片层割裂了:注意电路地与机壳地之间间距2MM:RX

上方向差分对没有包地处理,应尽量单对差分对包地处理电源信号走线加粗多处飞线没有连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/i

人类诞生至今,已有300多万年,在此过程中我们遇到了不少疾病难以解决,其中最大的病情莫过于“癌症”,可以说是“顽疾难医”。近日,国资小新官微发文表示:中核集团中国原子能科学研究院基于强流回旋加速器的硼中子俘获治疗(BNCT)样机研制成功,并

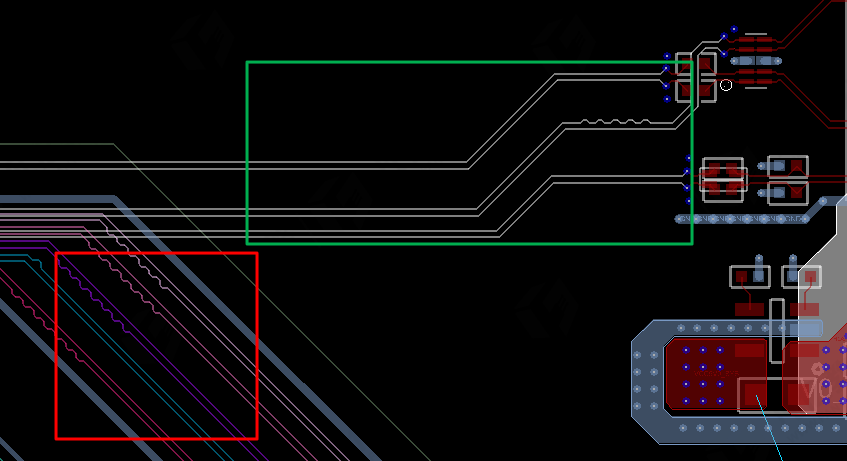

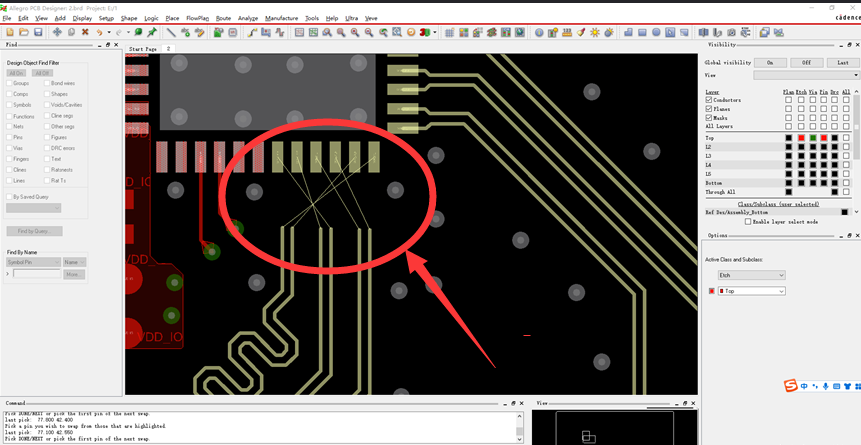

很多电子初学者在使用CadeNCe Allegro进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

射频(Radio FrequeNCy,RF)电路在现代电子领域中扮演着至关重要的角色,涵盖了广泛的应用,从通信系统到雷达和射频识别(RFID)等。在高速PCB设计中,射频电路的分析和处理是一项具有挑战性的任务。本文将介绍高速PCB设计中常见

CadeNCe allegro学习笔记第一节 启动与板框的制作1、启动操作启动PCB Editor图标,弹出对话框后选择Allegro PCB Designer后择OK进入界面。 选择File文件菜单选择New新建弹出下面对话框。设置

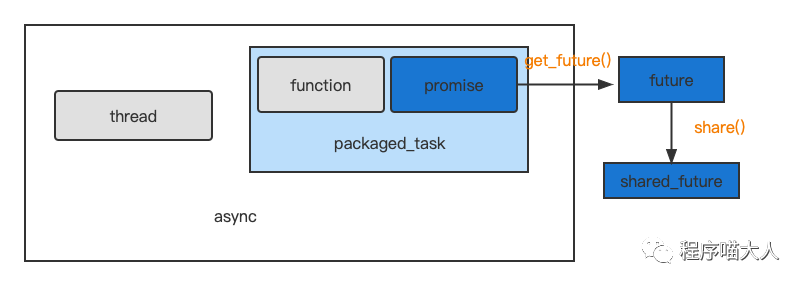

并发编程一般指多线程编程,C 11之后关于多线程编程有几个高级API:std::threadstd::futurestd::shared_futurestd::promisestd::packaged_taskstd::asyNC可能很多人都搞不清楚它们之前有什么联系,可以直接看这张图:如果连它们

这里我想主要介绍下在C语言中是如何实现的面向对象。知道了C语言实现面向对象的方式,我们再联想下,C 中的class的运行原理是什么?首先我们来写一段C 的class,拿一个Student类来举例子:在头文件中,我定义一个Student类:#pragma oNCeclass Student {pu

扫码关注

扫码关注