- 全部

- 默认排序

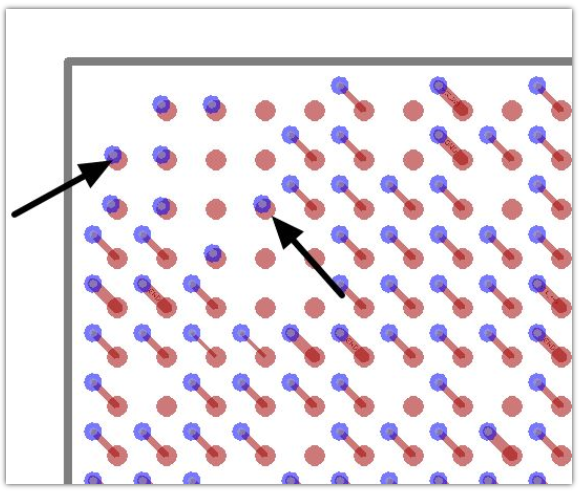

对于BGA扇孔,同样过孔不宜打孔在焊盘上,推荐打孔在两个焊盘的中间位置。很多工程师为了出线方便,随意挪动BGA里面过孔的位置,甚至打在焊盘上面,如图1所示,从而造成BGA区域过孔不规则,易造成后期焊接虚焊的问题,同时可能破坏平面完整性。图1

在仿真模拟软件中,ADS无疑是应用最广泛的,ADS全称为AdvaNCed Design System,由美国Keysight Technologies公司研发的EDA软件,主要面向射频、微波电路的设计、仿真和验证。下面将聊聊ADS仿真,希望

這篇文章將示範如何使用預設的評價函數(merit fuNCtion)工具和IMSF操作數(operand)對任意面進行優化。作者 Nam-Hyong Kim下载範例檔案簡介在模擬軟體中建構光學系統時,有時會必須對特定中間面(intermed

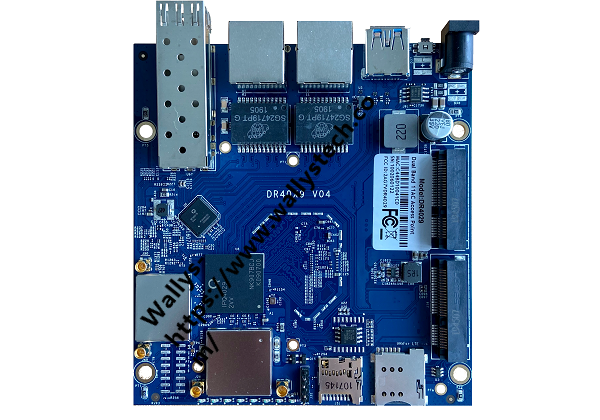

IPQ4019 and IPQ4029 are both system-on-chips (SoCs) developed by Qualcomm for use in networking devices such as routers,

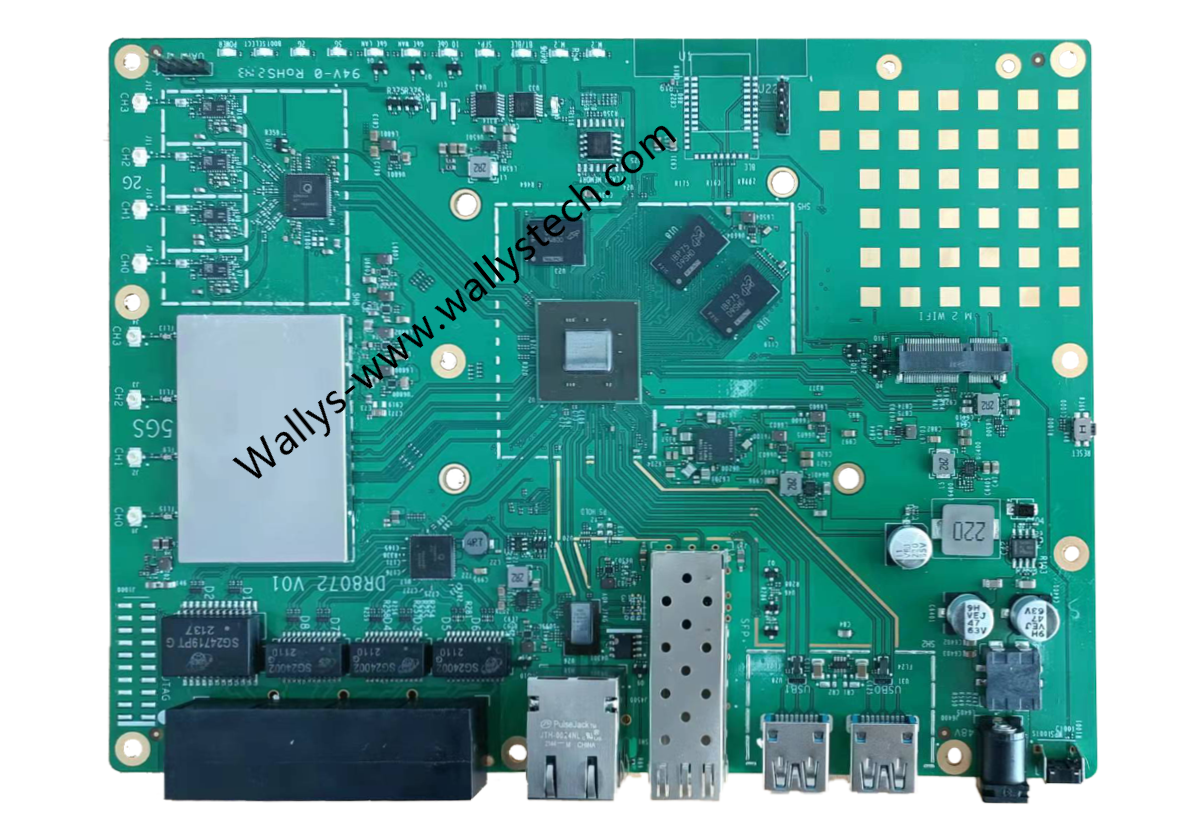

The IPQ8072 and IPQ8072A are both powerful networking SoCs (System-on-Chip) designed by Qualcomm for high-performaNCe ro

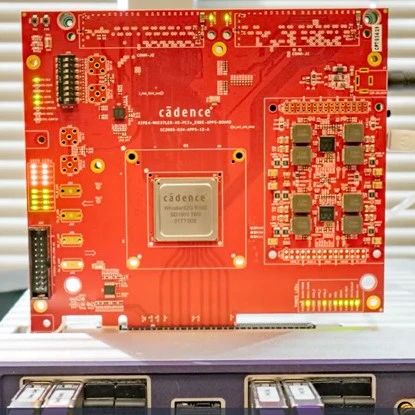

从规范草案到被 PCI-SIG 列入集成商的合规目录需要经历数年。初步 PCIe 5.0 规范于 2017 年 6 月公布,最终规范于 2019 年 5 月发布,第一次正式合规研讨会于 2022 年 4 月举行。如此漫长的过程说明了所开发的产品以及支持这些产品所需的生态系统非常复杂。CadeNCe

点击上方名片关注了解更多很多小公司,高校和研究所都喜欢使用AD,它确实也比较简单,且容易上手。然而一些同行和很多大公司都是一直用CadeNCe,并且说它有多么香。在高端PCB设计领域,CadeNCe是当前市场上主流高端软件供应商之一,其产品以卓越的性能备受各大企业的青睐。总觉得这个软件在PCB行

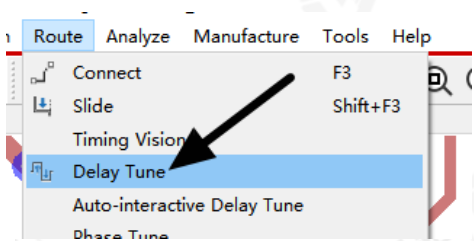

在PCB设计中做等长时,常常会用到蛇形走线,下面就介绍一下如何进行蛇形走线及相关设置:执行菜单面临Route-Delay Tune,在Options进行相关设置,其中Style是蛇形等长的样式,Gap一般设置为3倍线宽,Corners角度一

在EDA工具里,Mentor Pads和CadeNCe Allegro是电子工程师常用的软件,在进行PCB设计时,经常会和其他人共同参与项目,如果遇见了将Allegro电路板文件转换为Pads文件格式该如何做?这篇文或许能帮上你!1、准备工

Qualcomm Wi-Fi 7 network chip solutions IPQ9574 and IPQ9554 are advaNCed wireless connectivity solutions developed by Qu

扫码关注

扫码关注