- 全部

- 默认排序

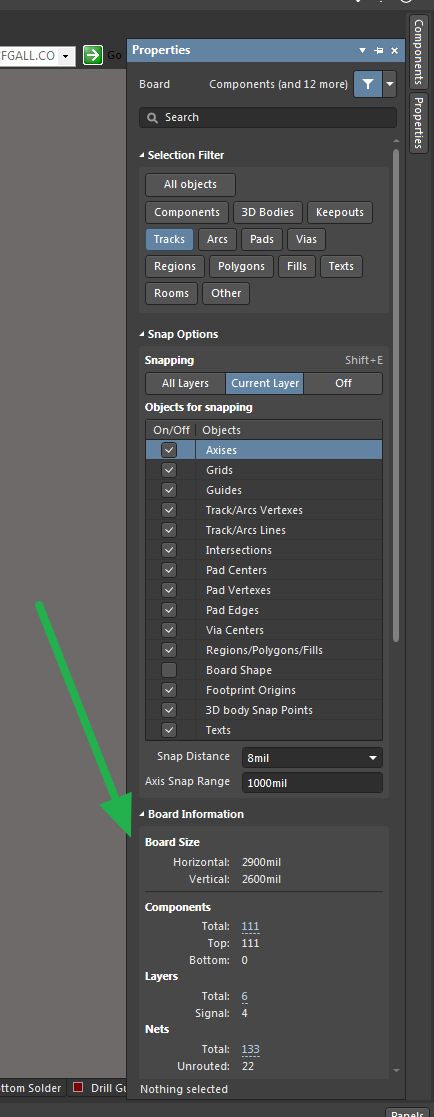

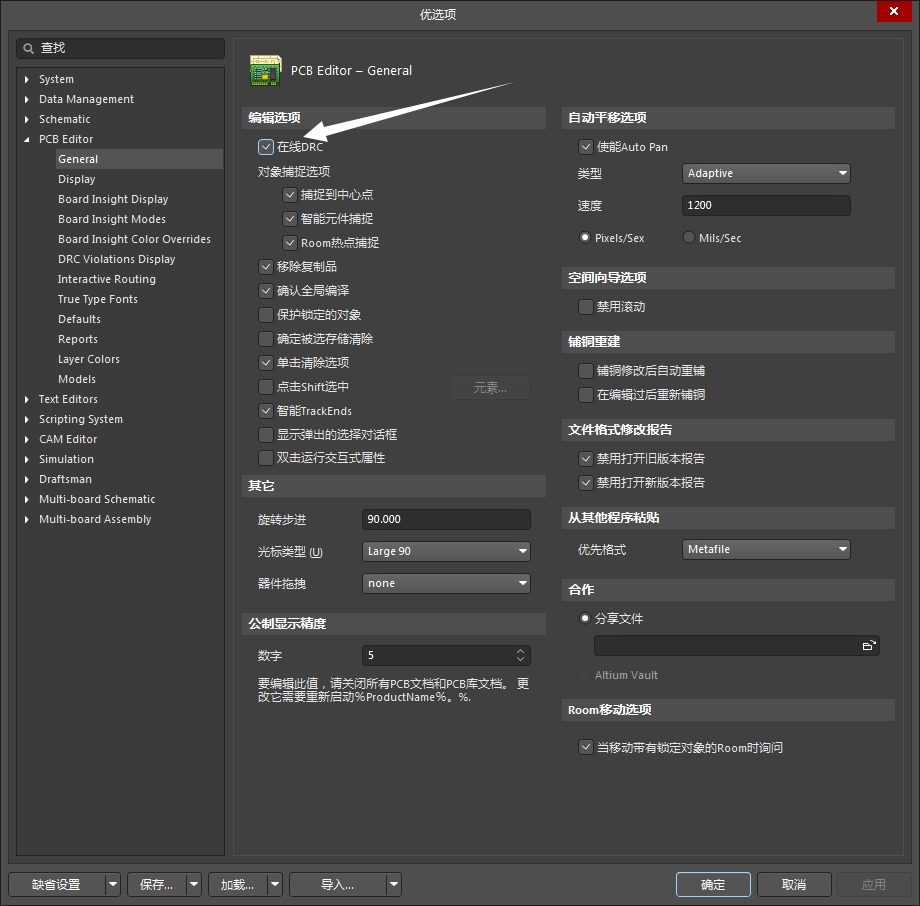

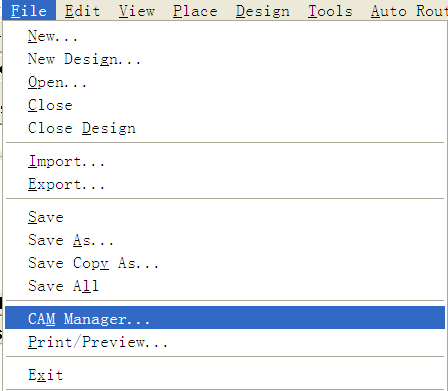

Ad19由于做了更新的改动,所以我们对应的RB就不能进行管脚的查看,首先我们点击我的PCB界面,然后我们点击我们的PCB的空白处,我们点击一下,然后我们对应在我们的paneL 面板下面调用出我们的proprieties这个界面,这个和低版本不一样之处在于,高版本将prorieties这个界面替代了我们的PCB Inspertor.

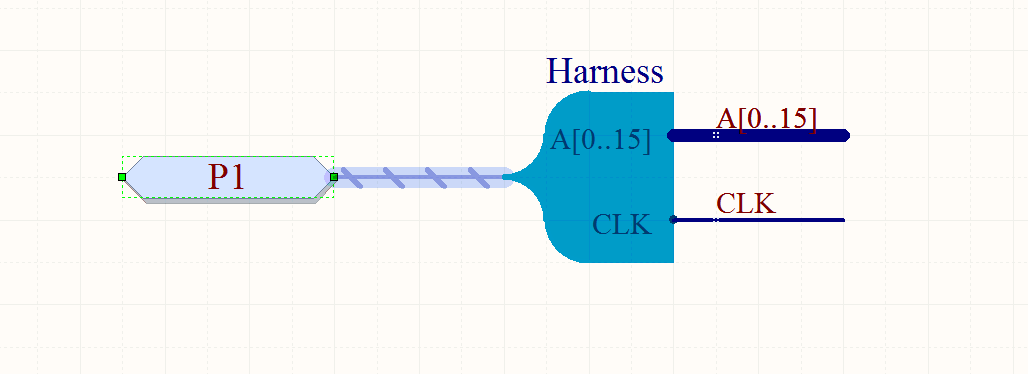

简化原理图线束的使用方法

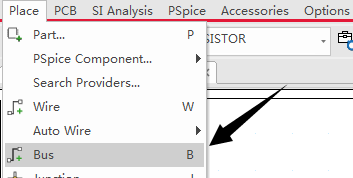

自ALtium Designer6.8之后的版本引入了信号线束(SignaL Harnesses)这个概念,并增加了放置、连接功能。信号线束主要用于原理图中连接不同的信号,可以把单条走线和总线汇集在一起并连接到其它信号线束上,这样能简化原理图设计,增强了设计的灵活性和流线性。

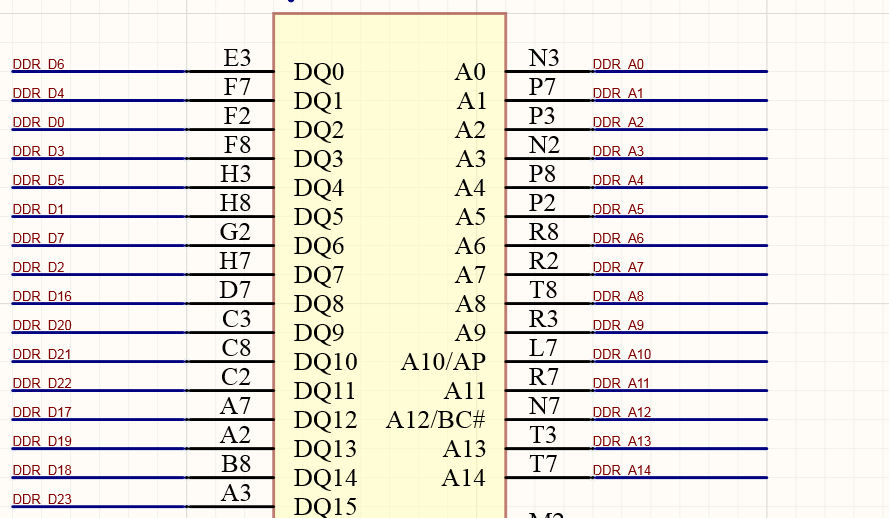

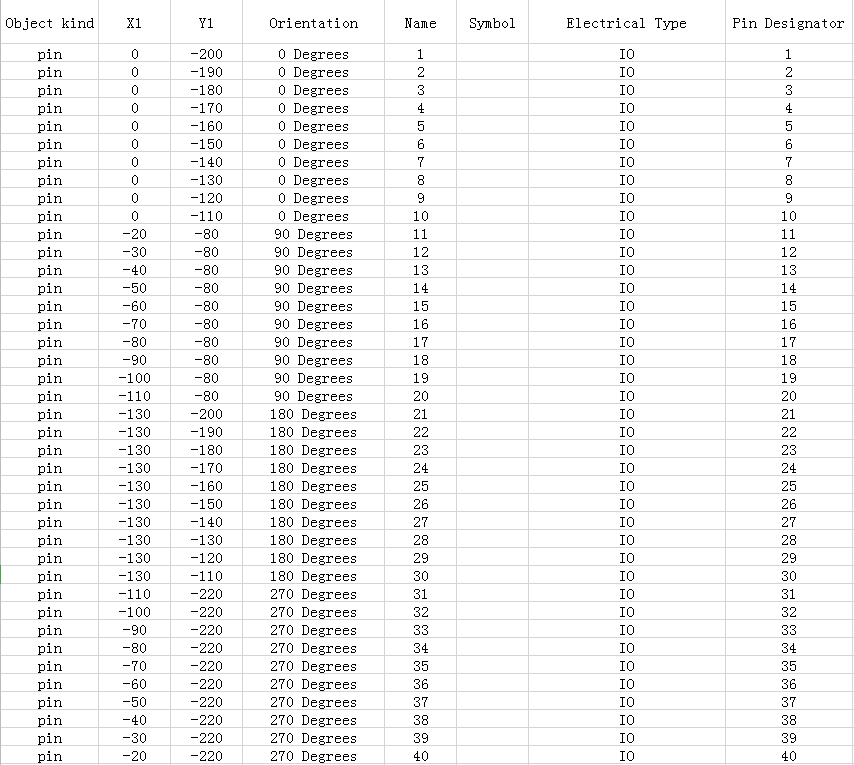

首先我们要在 ExceL 中建立一个表格,下图的 ExceL 为例子,自建,也可以先查找资料,有这方面的资料下载直接导入。下面8列是新加的包括 X、Y 坐标,方向,名字,电气属性,和管脚号等。 如果自建,上方的名字一定要对应,否则无法识别,会默认处理。

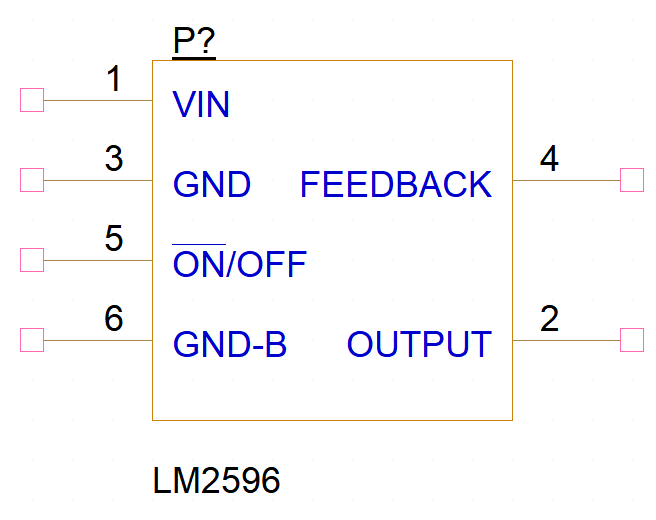

元件库开发环境及设计

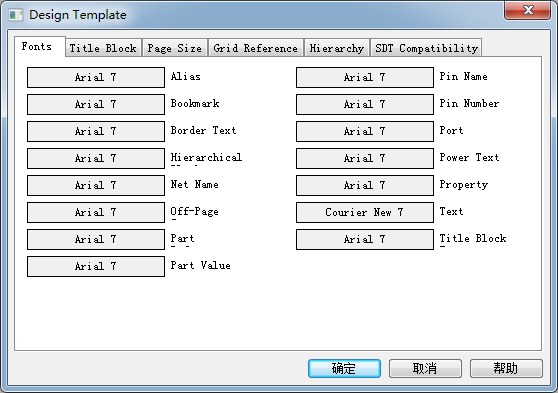

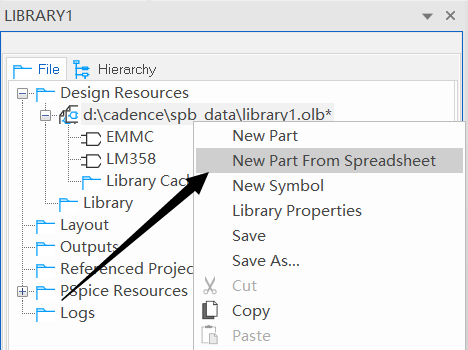

在用ALLegro Capture绘制原理图时,需要放置各种各样的元件。虽然Cadence ALLegro内置的元件库虽然很完备。但是难免会遇到找不到需要的元件的时候,因此在这种情况下便需要自己创建元件了。Cadence ALLegro提供了一个完整的创建元件的编辑器,可以根据自己的需要进行编辑或创建元件。本章将详细介绍如何创建原理图元件库。

在我们遇到引脚数量特别多的芯片时,此前用的创建元件的方法会显得特别的麻烦,且费时费力,也会容易出现错误,这时我们可以通过Capture导入ExceL表格的方式来方创建元件

扫码关注

扫码关注