- 全部

- 默认排序

在用Logic软件来绘制原理图时,首先要把整个图页上的格点设置好。设计格点可以设定一个栅格大小,用来确定对象在原理图当中每移动一步的格点数。显示格点设置可以为绘制线条、元件和连线提供一个可见的引导。

在我们进行原理图设计与元件库设计的时候,总会应用到格点的设置以及推荐设置值是多少。如果原理图与元件库中的格点设置相同,后期的原理图编译会少报错很多警告,那么我们就以AD19去设置格点大小及推荐值设定。

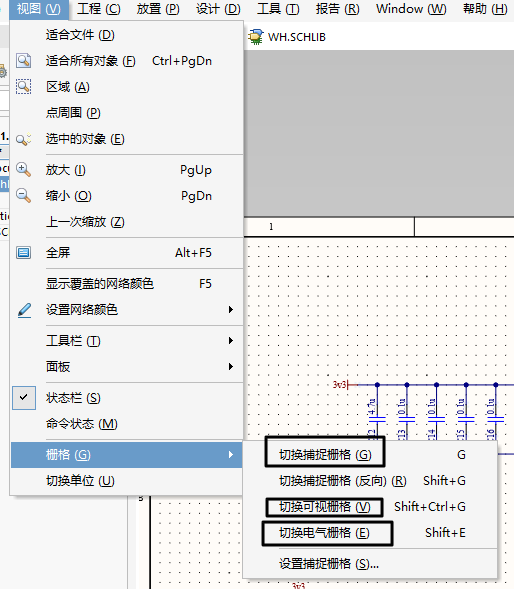

本视频采用Altium designer19 跟大家分享关于我们的View菜单栏下的各个命令的具体的含义,包括我们的视图的放大,视图的切换,工具栏的调用和隐藏,格点的设置等等的操作注意事项和认识。

本视频采用我们的Altium designer 19 关于我们的原理图的设计,主要讲解关于我们的格点的设置,同时针对与grid off这个报错我们如何进行对应的修改和处理,以及常用的格点的大小的设置。

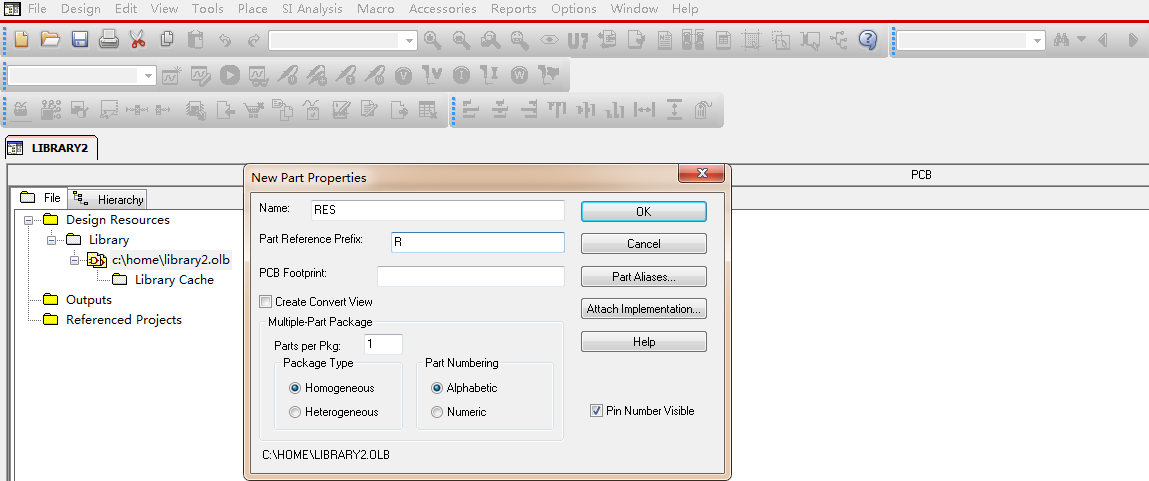

我们以一个电阻的封装为例,详细讲解创建一个简单分立元器件步骤:第一步,按照我们前面的问答中详细介绍,新建一个库文件,如图2-11所示,填写名称为RES,起始名称为R,PCB封装那一栏先可以不用填写,分立器件,Part选择1即可,其它按照默认设置; 图2-11 新建RES的库文件是示意图第二步,在弹出的R?的虚线框,在右侧栏选择Place Rectangle,绘制一个合适的矩形框在虚线内部,运用菜单栏上的Snap To Grid,关掉格点,将矩形框调整到合适的位置,然后将虚线框缩小至跟矩

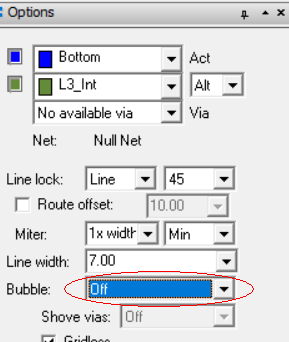

allegro在布线过程中,根据个人习惯有多种避让方式可以选择,不管采用那种方式,都需要经过优化才能使pcb布线更符合设计要求,推荐交叉使用以下方式进行布线。(1)使用off方式进行布线,可能导致很多DRC的产生,把网络连接好后,需要把DRC都消除掉。优化时需要把格点设小,使用微调推挤或重新布线方式,优点是布线可根据个人的意愿进行,布线速度快;缺点是优化时需要花费

在用AD软件进行某些软件操作时,经常需要对格点进行设置,在AD中有电气栅格、捕捉删格、可视栅格这三种栅格,那么这几种栅格有什么区别呢?

我们在进行原理图设计或者元件库绘制的时候,总觉得后面背景的栅格不是很清楚,不是很醒目。它并不是可视栅格隐藏了,但就是看起来不太清楚格点在哪里?我们的元器件或者管脚到底放置在格点上没,这对于我们原理图的设计和元件库的绘制非常的不方便。那么,我们为了让他更加清晰与醒目,到底应该如何设置它呢?

扫码关注

扫码关注