随着时代发展,高速PCB异军突起,以惊人速度成为了PCB设计的主力军,无数人选择成为高速PCB工程师,在项目中承担着重要的角色和责任,那么你知道高速PCB工程师平常做什么,在项目中具体负责做什么吗?下面来看看吧!

1、高速信号设计:从DDR到100G+的硬核规则

①DDR4/5布线规范:

T型拓扑:线长公差±5mil,间距≥3倍线宽,阻抗50Ω±10%。

VREF电容布局:距离DDR芯片≤200mil,优先采用0201封装(风华高科C系列)。

②PCIe 4.0/5.0设计:

差分对阻抗:85Ω±5%(内层带状线),长度匹配公差±1ps(0.06mm)。

过孔反焊盘处理:直径比过孔大8mil,避免阻抗突变(华为海思设计规范)。

③25G/100G光模块设计:

使用Megtron 6板材(生益科技S1145替代),损耗角正切≤0.002@10GHz。

金手指镀金厚度≥0.8μm(符合中航光电连接器标准)。

2、叠层与阻抗控制:成本与性能的博弈

①国产板材实战方案

②阻抗计算规则

差分对:线宽/间距=5/5mil(内层),4/6mil(表层),介厚误差≤±5%。

单端信号:50Ω控制需满足线宽=0.6×介厚(FR4板材)。

3、电源完整性设计:国产芯片的驯化之道

①国产电源方案实战

②去耦电容布局铁律

0.1μF陶瓷电容:距离芯片电源引脚≤200mil,优先使用国产宇阳0402封装。

钽电容:耐压降额50%,采用宏达电子TANTAMOUNT系列。

4、仿真验证:从理论到量产的死亡峡谷

①HyperLynx SI:

DDR4眼图仿真:眼高≥240mV,眼宽≥0.7UI(华为海思验收标准)。

串扰分析:相邻信号近端串扰≤5%。

②Sigrity PowerDC:

压降分析:3.3V网络压降≤2%(满载电流20A场景)。

电流密度:铜箔电流密度≤35A/mm²(持续工作条件)。

③HFSS 3D建模:

连接器S参数提取:25Gbps插损≤-2dB/inch,回损≥-15dB。

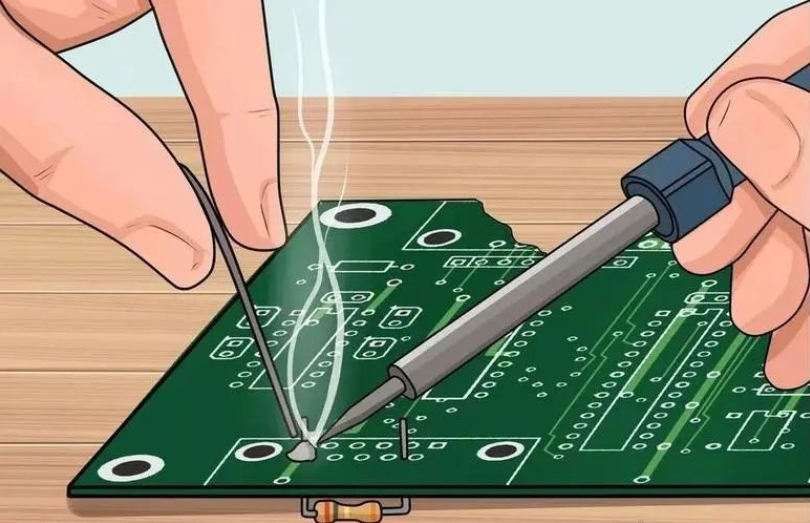

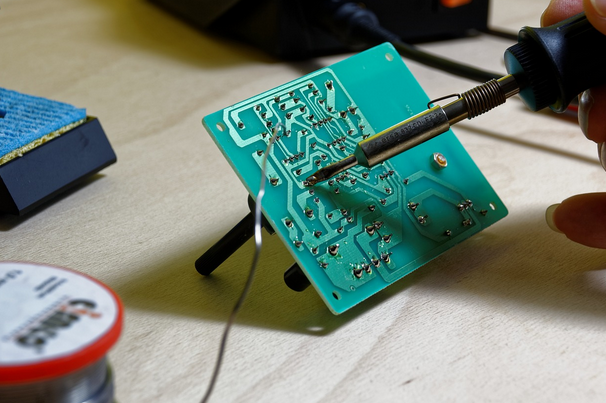

5、工厂对接:深南电路/兴森快捷的潜规则

①Gerber文件:

阻焊桥宽度≥4mil(华秋DFM强制要求),BGA区域阻焊开窗扩大0.1mm。

金手指区域单独输出为.GTL层,标注"Gold Fingers"(深南电路工艺规范)。

②钻孔文件:

盲埋孔标注:使用ALT_<层对>命名规则(如ALT_1-3表示1-3层盲孔)。

孔铜厚度:机械钻孔≥18μm,激光钻孔≥12μm(兴森快捷Class 3标准)。

6、国产EDA协同:突围卡脖子困局

①原理图阶段:

使用立创EDA绘制基础电路,导出Allegro网表时需转换器件属性(如Value→Part Number)。

②仿真阶段:

华大九天Empyrean ALPS与Cadence Sigrity联合仿真,通过CSV格式传递S参数。

③生产准备:

用华秋DFM一键生成《可制造性报告》,重点检查线宽/间距、孔铜、阻焊桥。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注